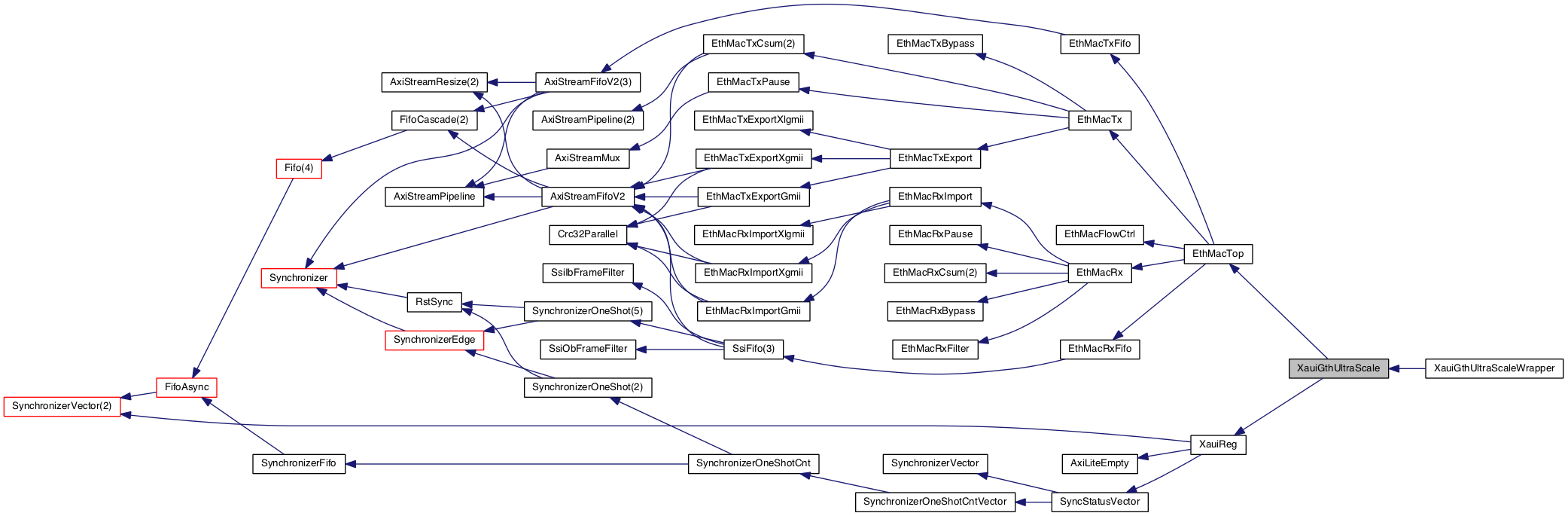

Inheritance diagram for XauiGthUltraScale:

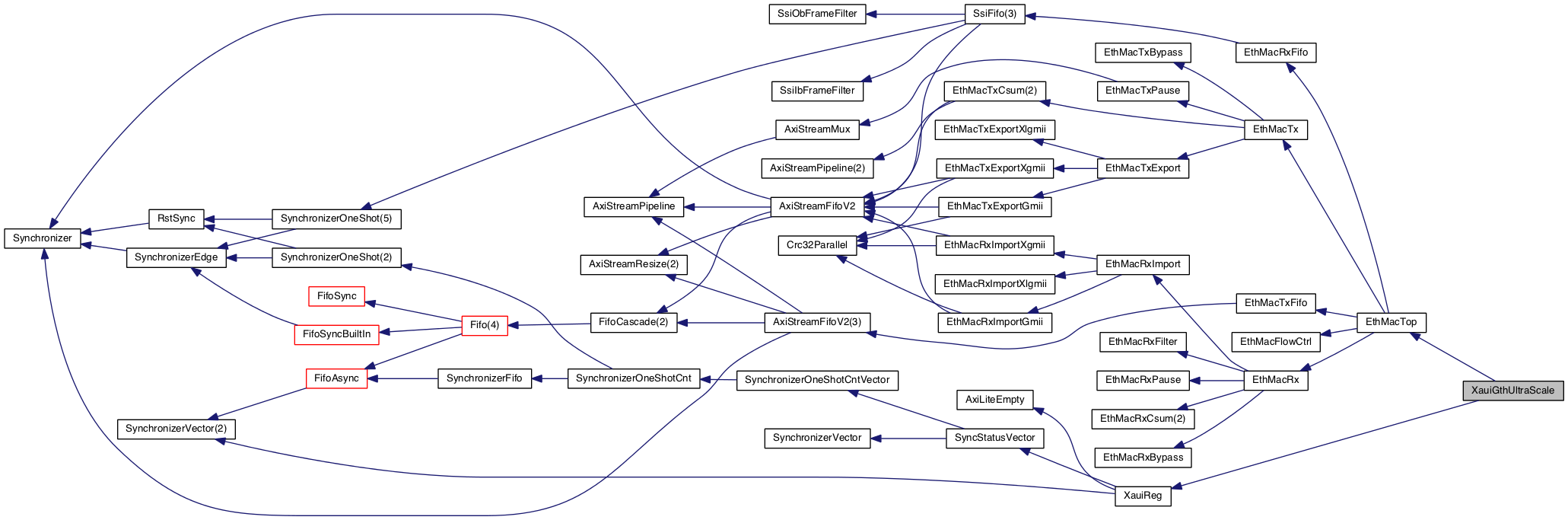

Inheritance diagram for XauiGthUltraScale: Collaboration diagram for XauiGthUltraScale:

Collaboration diagram for XauiGthUltraScale:Entities | |

| mapping | architecture |

Libraries | |

| ieee | |

| unisim | |

Use Clauses | |

| std_logic_1164 | |

| StdRtlPkg | Package <StdRtlPkg> |

| AxiStreamPkg | Package <AxiStreamPkg> |

| AxiLitePkg | Package <AxiLitePkg> |

| XauiPkg | Package <XauiPkg> |

| EthMacPkg | Package <EthMacPkg> |

| vcomponents | |

Generics | |

| TPD_G | time := 1 ns |

| XAUI_20GIGE_G | boolean := false |

| REF_CLK_FREQ_G | real := 156 . 25E + 6 |

| EN_AXI_REG_G | boolean := false |

| AXI_ERROR_RESP_G | slv ( 1 downto 0 ) := AXI_RESP_SLVERR_C |

| AXIS_CONFIG_G | AxiStreamConfigType := AXI_STREAM_CONFIG_INIT_C |

Ports | |

| localMac | in slv ( 47 downto 0 ) := MAC_ADDR_INIT_C |

| dmaClk | in sl |

| dmaRst | in sl |

| dmaIbMaster | out AxiStreamMasterType |

| dmaIbSlave | in AxiStreamSlaveType |

| dmaObMaster | in AxiStreamMasterType |

| dmaObSlave | out AxiStreamSlaveType |

| axiLiteClk | in sl := ' 0 ' |

| axiLiteRst | in sl := ' 0 ' |

| axiLiteReadMaster | in AxiLiteReadMasterType := AXI_LITE_READ_MASTER_INIT_C |

| axiLiteReadSlave | out AxiLiteReadSlaveType |

| axiLiteWriteMaster | in AxiLiteWriteMasterType := AXI_LITE_WRITE_MASTER_INIT_C |

| axiLiteWriteSlave | out AxiLiteWriteSlaveType |

| extRst | in sl |

| phyClk | out sl |

| phyRst | out sl |

| phyReady | out sl |

| gtTxPreCursor | in slv ( 19 downto 0 ) := ( others = > ' 0 ' ) |

| gtTxPostCursor | in slv ( 19 downto 0 ) := ( others = > ' 0 ' ) |

| gtTxDiffCtrl | in slv ( 15 downto 0 ) := x " CCCC " |

| gtRxPolarity | in slv ( 3 downto 0 ) := x " 0 " |

| gtTxPolarity | in slv ( 3 downto 0 ) := x " 0 " |

| refClk | in sl |

| gtTxP | out slv ( 3 downto 0 ) |

| gtTxN | out slv ( 3 downto 0 ) |

| gtRxP | in slv ( 3 downto 0 ) |

| gtRxN | in slv ( 3 downto 0 ) |

Detailed Description

- See also

- entity

Definition at line 32 of file XauiGthUltraScale.vhd.

Member Data Documentation

◆ TPD_G

|

Generic |

Definition at line 34 of file XauiGthUltraScale.vhd.

◆ XAUI_20GIGE_G

|

Generic |

Definition at line 36 of file XauiGthUltraScale.vhd.

◆ REF_CLK_FREQ_G

|

Generic |

Definition at line 37 of file XauiGthUltraScale.vhd.

◆ EN_AXI_REG_G

|

Generic |

Definition at line 39 of file XauiGthUltraScale.vhd.

◆ AXI_ERROR_RESP_G

|

Generic |

Definition at line 40 of file XauiGthUltraScale.vhd.

◆ AXIS_CONFIG_G

Definition at line 42 of file XauiGthUltraScale.vhd.

◆ localMac

|

Port |

Definition at line 45 of file XauiGthUltraScale.vhd.

◆ dmaClk

Definition at line 47 of file XauiGthUltraScale.vhd.

◆ dmaRst

Definition at line 48 of file XauiGthUltraScale.vhd.

◆ dmaIbMaster

|

Port |

Definition at line 49 of file XauiGthUltraScale.vhd.

◆ dmaIbSlave

|

Port |

Definition at line 50 of file XauiGthUltraScale.vhd.

◆ dmaObMaster

|

Port |

Definition at line 51 of file XauiGthUltraScale.vhd.

◆ dmaObSlave

|

Port |

Definition at line 52 of file XauiGthUltraScale.vhd.

◆ axiLiteClk

|

Port |

Definition at line 54 of file XauiGthUltraScale.vhd.

◆ axiLiteRst

|

Port |

Definition at line 55 of file XauiGthUltraScale.vhd.

◆ axiLiteReadMaster

Definition at line 56 of file XauiGthUltraScale.vhd.

◆ axiLiteReadSlave

|

Port |

Definition at line 57 of file XauiGthUltraScale.vhd.

◆ axiLiteWriteMaster

Definition at line 58 of file XauiGthUltraScale.vhd.

◆ axiLiteWriteSlave

|

Port |

Definition at line 59 of file XauiGthUltraScale.vhd.

◆ extRst

Definition at line 61 of file XauiGthUltraScale.vhd.

◆ phyClk

Definition at line 62 of file XauiGthUltraScale.vhd.

◆ phyRst

Definition at line 63 of file XauiGthUltraScale.vhd.

◆ phyReady

Definition at line 64 of file XauiGthUltraScale.vhd.

◆ gtTxPreCursor

|

Port |

Definition at line 66 of file XauiGthUltraScale.vhd.

◆ gtTxPostCursor

|

Port |

Definition at line 67 of file XauiGthUltraScale.vhd.

◆ gtTxDiffCtrl

|

Port |

Definition at line 68 of file XauiGthUltraScale.vhd.

◆ gtRxPolarity

|

Port |

Definition at line 69 of file XauiGthUltraScale.vhd.

◆ gtTxPolarity

|

Port |

Definition at line 70 of file XauiGthUltraScale.vhd.

◆ refClk

Definition at line 72 of file XauiGthUltraScale.vhd.

◆ gtTxP

Definition at line 73 of file XauiGthUltraScale.vhd.

◆ gtTxN

Definition at line 74 of file XauiGthUltraScale.vhd.

◆ gtRxP

Definition at line 75 of file XauiGthUltraScale.vhd.

◆ gtRxN

Definition at line 76 of file XauiGthUltraScale.vhd.

◆ ieee

|

Library |

Definition at line 18 of file XauiGthUltraScale.vhd.

◆ std_logic_1164

|

Package |

Definition at line 19 of file XauiGthUltraScale.vhd.

◆ StdRtlPkg

|

Package |

Definition at line 21 of file XauiGthUltraScale.vhd.

◆ AxiStreamPkg

|

Package |

Definition at line 22 of file XauiGthUltraScale.vhd.

◆ AxiLitePkg

|

Package |

Definition at line 23 of file XauiGthUltraScale.vhd.

◆ XauiPkg

|

Package |

Definition at line 24 of file XauiGthUltraScale.vhd.

◆ EthMacPkg

|

Package |

Definition at line 25 of file XauiGthUltraScale.vhd.

◆ unisim

|

Library |

Definition at line 27 of file XauiGthUltraScale.vhd.

◆ vcomponents

|

Package |

Definition at line 28 of file XauiGthUltraScale.vhd.

The documentation for this class was generated from the following file:

- ethernet/XauiCore/gthUltraScale/rtl/XauiGthUltraScale.vhd