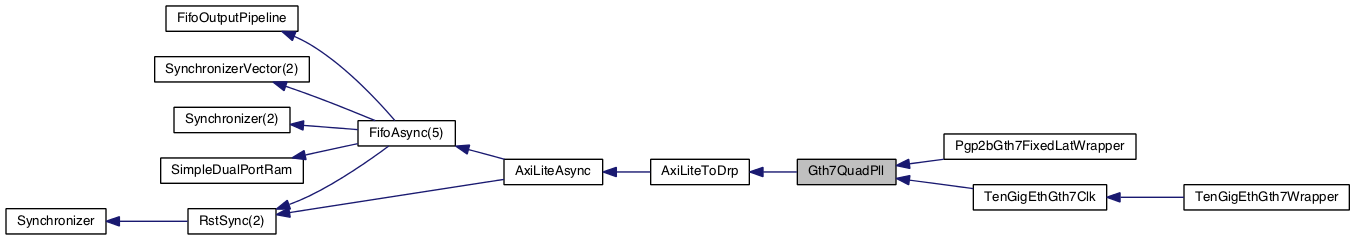

Inheritance diagram for Gth7QuadPll:

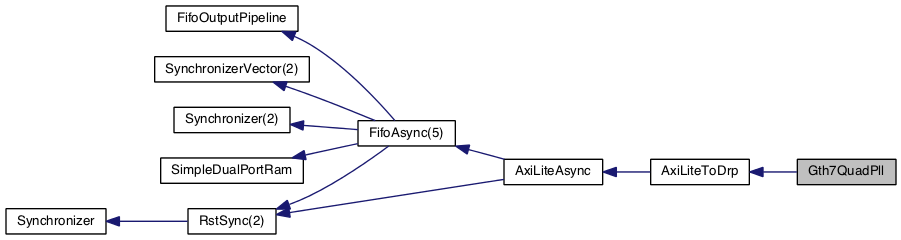

Inheritance diagram for Gth7QuadPll: Collaboration diagram for Gth7QuadPll:

Collaboration diagram for Gth7QuadPll:Entities | |

| mapping | architecture |

Libraries | |

| ieee | |

| unisim | |

Use Clauses | |

| std_logic_1164 | |

| numeric_std | |

| StdRtlPkg | Package <StdRtlPkg> |

| AxiLitePkg | Package <AxiLitePkg> |

| vcomponents | |

Generics | |

| TPD_G | time := 1 ns |

| AXI_ERROR_RESP_G | slv ( 1 downto 0 ) := AXI_RESP_DECERR_C |

| SIM_RESET_SPEEDUP_G | string := " TRUE " |

| SIM_VERSION_G | string := " 2.0 " |

| QPLL_CFG_G | bit_vector := x " 04801C7 " |

| QPLL_REFCLK_SEL_G | bit_vector := " 001 " |

| QPLL_FBDIV_G | bit_vector := " 0100100000 " |

| QPLL_FBDIV_RATIO_G | bit := ' 1 ' |

| QPLL_REFCLK_DIV_G | integer := 1 |

Ports | |

| qPllRefClk | in sl |

| qPllOutClk | out sl |

| qPllOutRefClk | out sl |

| qPllLock | out sl |

| qPllLockDetClk | in sl |

| qPllRefClkLost | out sl |

| qPllPowerDown | in sl := ' 0 ' |

| qPllReset | in sl |

| axilClk | in sl := ' 0 ' |

| axilRst | in sl := ' 0 ' |

| axilReadMaster | in AxiLiteReadMasterType := AXI_LITE_READ_MASTER_INIT_C |

| axilReadSlave | out AxiLiteReadSlaveType |

| axilWriteMaster | in AxiLiteWriteMasterType := AXI_LITE_WRITE_MASTER_INIT_C |

| axilWriteSlave | out AxiLiteWriteSlaveType |

Detailed Description

- See also

- entity

Definition at line 30 of file Gth7QuadPll.vhd.

Member Data Documentation

◆ TPD_G

|

Generic |

Definition at line 32 of file Gth7QuadPll.vhd.

◆ AXI_ERROR_RESP_G

|

Generic |

Definition at line 33 of file Gth7QuadPll.vhd.

◆ SIM_RESET_SPEEDUP_G

|

Generic |

Definition at line 34 of file Gth7QuadPll.vhd.

◆ SIM_VERSION_G

|

Generic |

Definition at line 35 of file Gth7QuadPll.vhd.

◆ QPLL_CFG_G

|

Generic |

Definition at line 36 of file Gth7QuadPll.vhd.

◆ QPLL_REFCLK_SEL_G

|

Generic |

Definition at line 37 of file Gth7QuadPll.vhd.

◆ QPLL_FBDIV_G

|

Generic |

Definition at line 38 of file Gth7QuadPll.vhd.

◆ QPLL_FBDIV_RATIO_G

|

Generic |

Definition at line 39 of file Gth7QuadPll.vhd.

◆ QPLL_REFCLK_DIV_G

|

Generic |

Definition at line 40 of file Gth7QuadPll.vhd.

◆ qPllRefClk

|

Port |

Definition at line 42 of file Gth7QuadPll.vhd.

◆ qPllOutClk

|

Port |

Definition at line 43 of file Gth7QuadPll.vhd.

◆ qPllOutRefClk

|

Port |

Definition at line 44 of file Gth7QuadPll.vhd.

◆ qPllLock

Definition at line 45 of file Gth7QuadPll.vhd.

◆ qPllLockDetClk

|

Port |

Definition at line 46 of file Gth7QuadPll.vhd.

◆ qPllRefClkLost

|

Port |

Definition at line 47 of file Gth7QuadPll.vhd.

◆ qPllPowerDown

|

Port |

Definition at line 48 of file Gth7QuadPll.vhd.

◆ qPllReset

Definition at line 49 of file Gth7QuadPll.vhd.

◆ axilClk

Definition at line 51 of file Gth7QuadPll.vhd.

◆ axilRst

Definition at line 52 of file Gth7QuadPll.vhd.

◆ axilReadMaster

Definition at line 53 of file Gth7QuadPll.vhd.

◆ axilReadSlave

|

Port |

Definition at line 54 of file Gth7QuadPll.vhd.

◆ axilWriteMaster

Definition at line 55 of file Gth7QuadPll.vhd.

◆ axilWriteSlave

|

Port |

Definition at line 56 of file Gth7QuadPll.vhd.

◆ ieee

|

Library |

Definition at line 18 of file Gth7QuadPll.vhd.

◆ std_logic_1164

|

Package |

Definition at line 19 of file Gth7QuadPll.vhd.

◆ numeric_std

|

Package |

Definition at line 20 of file Gth7QuadPll.vhd.

◆ StdRtlPkg

|

Package |

Definition at line 22 of file Gth7QuadPll.vhd.

◆ AxiLitePkg

|

Package |

Definition at line 23 of file Gth7QuadPll.vhd.

◆ unisim

|

Library |

Definition at line 25 of file Gth7QuadPll.vhd.

◆ vcomponents

|

Package |

Definition at line 26 of file Gth7QuadPll.vhd.

The documentation for this class was generated from the following file:

- xilinx/7Series/gth7/rtl/Gth7QuadPll.vhd