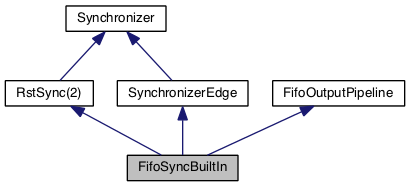

Inheritance diagram for FifoSyncBuiltIn:

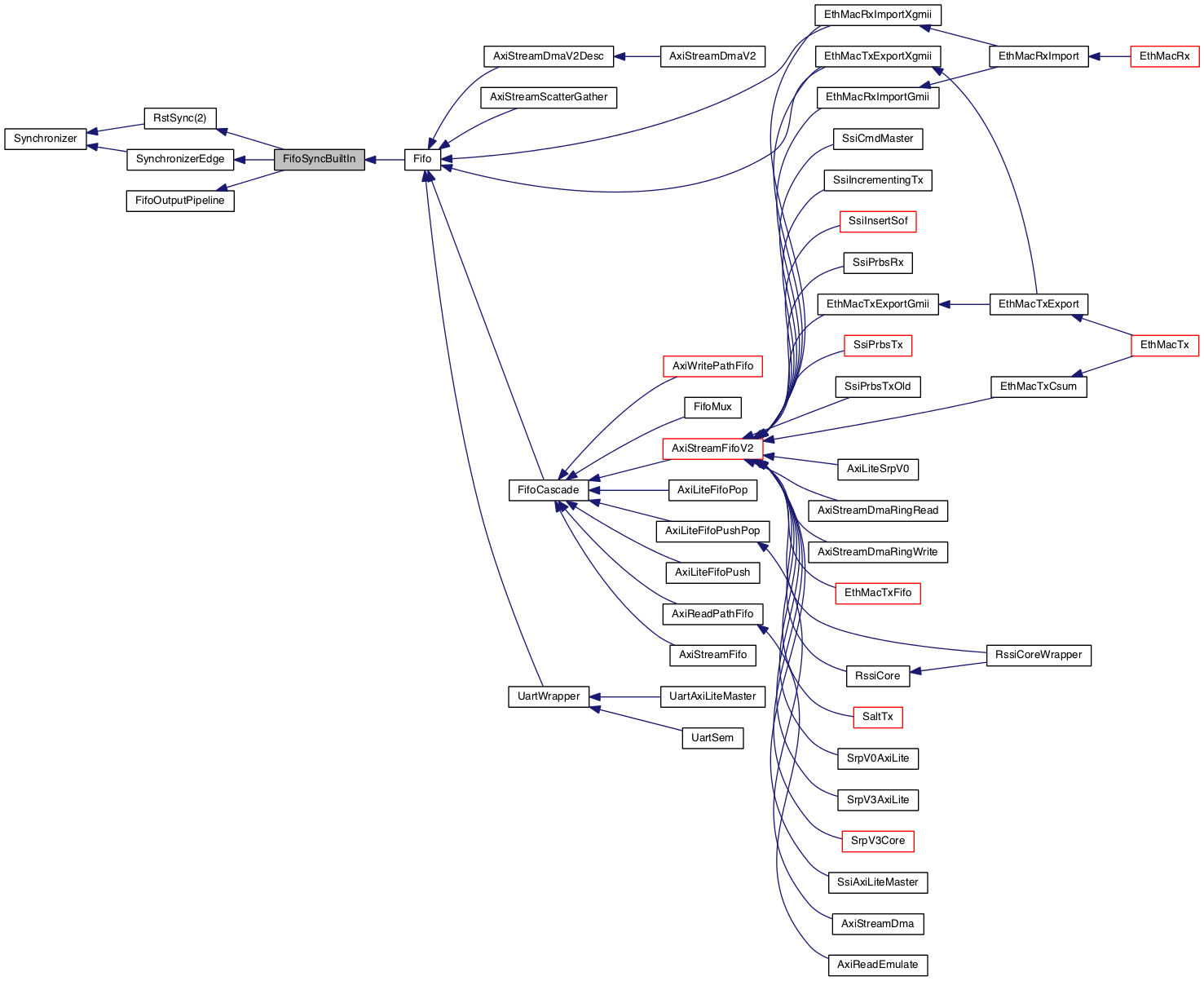

Inheritance diagram for FifoSyncBuiltIn: Collaboration diagram for FifoSyncBuiltIn:

Collaboration diagram for FifoSyncBuiltIn:Entities | |

| mapping | architecture |

Libraries | |

| ieee | |

| UNISIM | |

| UNIMACRO | |

Use Clauses | |

| std_logic_1164 | |

| std_logic_unsigned | |

| std_logic_arith | |

| StdRtlPkg | Package <StdRtlPkg> |

| vcomponents | |

Generics | |

| TPD_G | time := 1 ns |

| RST_POLARITY_G | sl := ' 1 ' |

| FWFT_EN_G | boolean := false |

| USE_DSP48_G | string := " no " |

| XIL_DEVICE_G | string := " 7SERIES " |

| PIPE_STAGES_G | natural range 0 to 16 := 0 |

| DATA_WIDTH_G | integer range 1 to 72 := 18 |

| ADDR_WIDTH_G | integer range 9 to 13 := 10 |

| FULL_THRES_G | integer range 1 to 8190 := 1 |

| EMPTY_THRES_G | integer range 1 to 8190 := 1 |

Ports | |

| rst | in sl := ' 0 ' |

| clk | in sl |

| wr_en | in sl |

| rd_en | in sl |

| din | in slv ( DATA_WIDTH_G - 1 downto 0 ) |

| dout | out slv ( DATA_WIDTH_G - 1 downto 0 ) |

| data_count | out slv ( ADDR_WIDTH_G - 1 downto 0 ) |

| wr_ack | out sl |

| valid | out sl |

| overflow | out sl |

| underflow | out sl |

| prog_full | out sl |

| prog_empty | out sl |

| almost_full | out sl |

| almost_empty | out sl |

| not_full | out sl |

| full | out sl |

| empty | out sl |

Detailed Description

- See also

- entity

Definition at line 33 of file FifoSyncBuiltIn.vhd.

Member Data Documentation

◆ TPD_G

|

Generic |

Definition at line 35 of file FifoSyncBuiltIn.vhd.

◆ RST_POLARITY_G

|

Generic |

Definition at line 36 of file FifoSyncBuiltIn.vhd.

◆ FWFT_EN_G

|

Generic |

Definition at line 37 of file FifoSyncBuiltIn.vhd.

◆ USE_DSP48_G

|

Generic |

Definition at line 38 of file FifoSyncBuiltIn.vhd.

◆ XIL_DEVICE_G

|

Generic |

Definition at line 39 of file FifoSyncBuiltIn.vhd.

◆ PIPE_STAGES_G

|

Generic |

Definition at line 40 of file FifoSyncBuiltIn.vhd.

◆ DATA_WIDTH_G

|

Generic |

Definition at line 41 of file FifoSyncBuiltIn.vhd.

◆ ADDR_WIDTH_G

|

Generic |

Definition at line 42 of file FifoSyncBuiltIn.vhd.

◆ FULL_THRES_G

|

Generic |

Definition at line 43 of file FifoSyncBuiltIn.vhd.

◆ EMPTY_THRES_G

|

Generic |

Definition at line 44 of file FifoSyncBuiltIn.vhd.

◆ rst

Definition at line 46 of file FifoSyncBuiltIn.vhd.

◆ clk

Definition at line 47 of file FifoSyncBuiltIn.vhd.

◆ wr_en

Definition at line 48 of file FifoSyncBuiltIn.vhd.

◆ rd_en

Definition at line 49 of file FifoSyncBuiltIn.vhd.

◆ din

|

Port |

Definition at line 50 of file FifoSyncBuiltIn.vhd.

◆ dout

|

Port |

Definition at line 51 of file FifoSyncBuiltIn.vhd.

◆ data_count

|

Port |

Definition at line 52 of file FifoSyncBuiltIn.vhd.

◆ wr_ack

Definition at line 53 of file FifoSyncBuiltIn.vhd.

◆ valid

Definition at line 54 of file FifoSyncBuiltIn.vhd.

◆ overflow

Definition at line 55 of file FifoSyncBuiltIn.vhd.

◆ underflow

Definition at line 56 of file FifoSyncBuiltIn.vhd.

◆ prog_full

Definition at line 57 of file FifoSyncBuiltIn.vhd.

◆ prog_empty

|

Port |

Definition at line 58 of file FifoSyncBuiltIn.vhd.

◆ almost_full

|

Port |

Definition at line 59 of file FifoSyncBuiltIn.vhd.

◆ almost_empty

|

Port |

Definition at line 60 of file FifoSyncBuiltIn.vhd.

◆ not_full

Definition at line 61 of file FifoSyncBuiltIn.vhd.

◆ full

Definition at line 62 of file FifoSyncBuiltIn.vhd.

◆ empty

Definition at line 63 of file FifoSyncBuiltIn.vhd.

◆ ieee

|

Library |

Definition at line 18 of file FifoSyncBuiltIn.vhd.

◆ std_logic_1164

|

Package |

Definition at line 19 of file FifoSyncBuiltIn.vhd.

◆ std_logic_unsigned

|

Package |

Definition at line 20 of file FifoSyncBuiltIn.vhd.

◆ std_logic_arith

|

Package |

Definition at line 21 of file FifoSyncBuiltIn.vhd.

◆ StdRtlPkg

|

Package |

Definition at line 23 of file FifoSyncBuiltIn.vhd.

◆ UNISIM

|

Library |

Definition at line 25 of file FifoSyncBuiltIn.vhd.

◆ vcomponents

|

Package |

Definition at line 26 of file FifoSyncBuiltIn.vhd.

◆ UNIMACRO

|

Library |

Definition at line 28 of file FifoSyncBuiltIn.vhd.

The documentation for this class was generated from the following file:

- base/fifo/rtl/FifoSyncBuiltIn.vhd