- See also

- entity srp

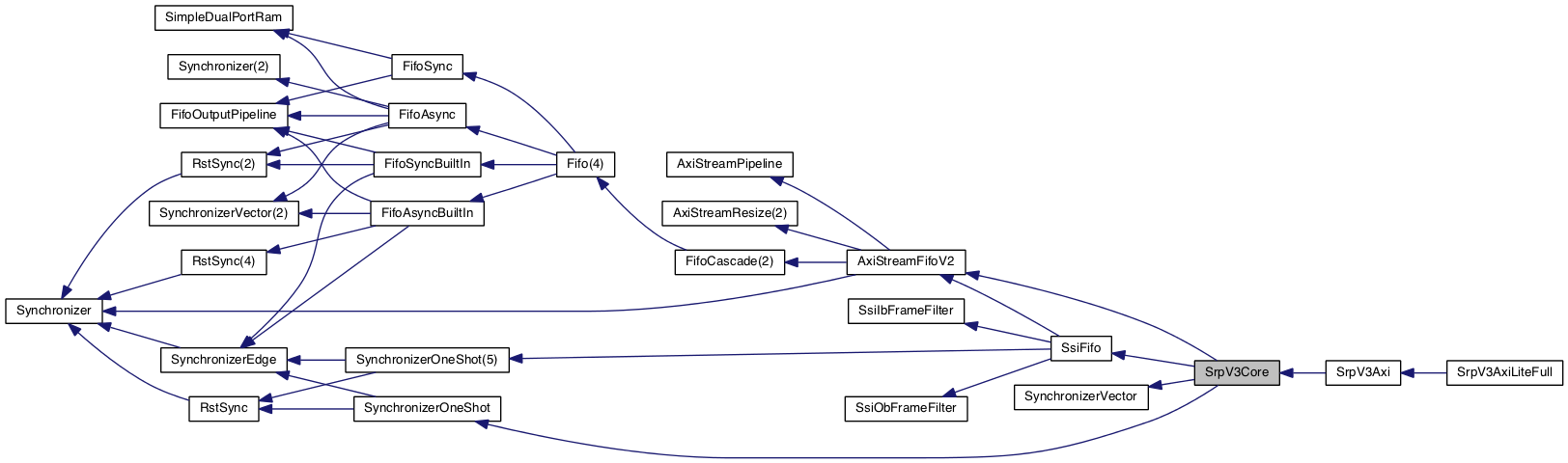

Inheritance diagram for SrpV3Core:

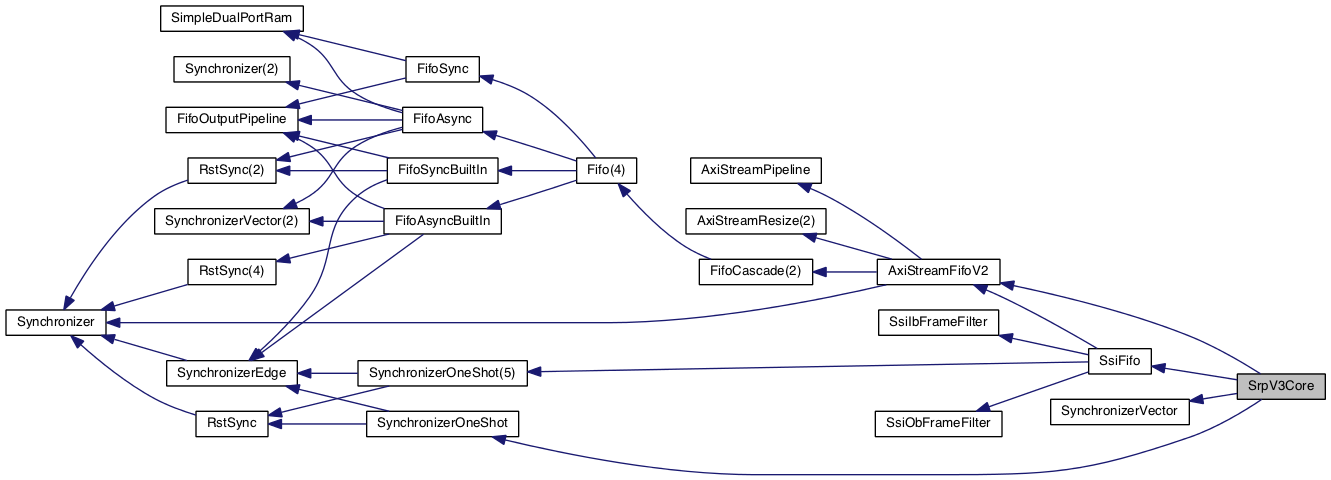

Inheritance diagram for SrpV3Core: Collaboration diagram for SrpV3Core:

Collaboration diagram for SrpV3Core:Entities | |

| rtl | architecture |

Libraries | |

| ieee | |

Use Clauses | |

| std_logic_1164 | |

| std_logic_arith | |

| std_logic_unsigned | |

| StdRtlPkg | Package <StdRtlPkg> |

| AxiStreamPkg | Package <AxiStreamPkg> |

| SsiPkg | Package <SsiPkg> |

| AxiLitePkg | Package <AxiLitePkg> |

| SrpV3Pkg | Package <SrpV3Pkg> |

Generics | |

| TPD_G | time := 1 ns |

| PIPE_STAGES_G | natural range 0 to 16 := 1 |

| FIFO_PAUSE_THRESH_G | positive range 1 to 511 := 256 |

| TX_VALID_THOLD_G | positive := 1 |

| SLAVE_READY_EN_G | boolean := false |

| GEN_SYNC_FIFO_G | boolean := false |

| ALTERA_SYN_G | boolean := false |

| ALTERA_RAM_G | string := " M9K " |

| SRP_CLK_FREQ_G | real := 156 . 25E + 6 |

| AXI_STREAM_CONFIG_G | AxiStreamConfigType := ssiAxiStreamConfig ( 2 ) |

| UNALIGNED_ACCESS_G | boolean := false |

| BYTE_ACCESS_G | boolean := false |

| WRITE_EN_G | boolean := true |

| READ_EN_G | boolean := true |

Ports | |

| sAxisClk | in sl |

| sAxisRst | in sl |

| sAxisMaster | in AxiStreamMasterType |

| sAxisSlave | out AxiStreamSlaveType |

| sAxisCtrl | out AxiStreamCtrlType |

| mAxisClk | in sl |

| mAxisRst | in sl |

| mAxisMaster | out AxiStreamMasterType |

| mAxisSlave | in AxiStreamSlaveType |

| srpClk | in sl |

| srpRst | in sl |

| srpReq | out SrpV3ReqType |

| srpAck | in SrpV3AckType |

| srpWrMaster | out AxiStreamMasterType |

| srpWrSlave | in AxiStreamSlaveType |

| srpRdMaster | in AxiStreamMasterType |

| srpRdSlave | out AxiStreamSlaveType |

Detailed Description

Definition at line 37 of file SrpV3Core.vhd.

Member Data Documentation

◆ TPD_G

|

Generic |

Definition at line 39 of file SrpV3Core.vhd.

◆ PIPE_STAGES_G

|

Generic |

Definition at line 40 of file SrpV3Core.vhd.

◆ FIFO_PAUSE_THRESH_G

|

Generic |

Definition at line 41 of file SrpV3Core.vhd.

◆ TX_VALID_THOLD_G

|

Generic |

Definition at line 42 of file SrpV3Core.vhd.

◆ SLAVE_READY_EN_G

|

Generic |

Definition at line 43 of file SrpV3Core.vhd.

◆ GEN_SYNC_FIFO_G

|

Generic |

Definition at line 44 of file SrpV3Core.vhd.

◆ ALTERA_SYN_G

|

Generic |

Definition at line 45 of file SrpV3Core.vhd.

◆ ALTERA_RAM_G

|

Generic |

Definition at line 46 of file SrpV3Core.vhd.

◆ SRP_CLK_FREQ_G

|

Generic |

Definition at line 47 of file SrpV3Core.vhd.

◆ AXI_STREAM_CONFIG_G

|

Generic |

Definition at line 48 of file SrpV3Core.vhd.

◆ UNALIGNED_ACCESS_G

|

Generic |

Definition at line 49 of file SrpV3Core.vhd.

◆ BYTE_ACCESS_G

|

Generic |

Definition at line 50 of file SrpV3Core.vhd.

◆ WRITE_EN_G

|

Generic |

Definition at line 51 of file SrpV3Core.vhd.

◆ READ_EN_G

|

Generic |

Definition at line 53 of file SrpV3Core.vhd.

◆ sAxisClk

Definition at line 56 of file SrpV3Core.vhd.

◆ sAxisRst

Definition at line 57 of file SrpV3Core.vhd.

◆ sAxisMaster

|

Port |

Definition at line 58 of file SrpV3Core.vhd.

◆ sAxisSlave

|

Port |

Definition at line 59 of file SrpV3Core.vhd.

◆ sAxisCtrl

|

Port |

Definition at line 60 of file SrpV3Core.vhd.

◆ mAxisClk

Definition at line 62 of file SrpV3Core.vhd.

◆ mAxisRst

Definition at line 63 of file SrpV3Core.vhd.

◆ mAxisMaster

|

Port |

Definition at line 64 of file SrpV3Core.vhd.

◆ mAxisSlave

|

Port |

Definition at line 65 of file SrpV3Core.vhd.

◆ srpClk

Definition at line 67 of file SrpV3Core.vhd.

◆ srpRst

Definition at line 68 of file SrpV3Core.vhd.

◆ srpReq

|

Port |

Definition at line 69 of file SrpV3Core.vhd.

◆ srpAck

|

Port |

Definition at line 70 of file SrpV3Core.vhd.

◆ srpWrMaster

|

Port |

Definition at line 71 of file SrpV3Core.vhd.

◆ srpWrSlave

|

Port |

Definition at line 72 of file SrpV3Core.vhd.

◆ srpRdMaster

|

Port |

Definition at line 73 of file SrpV3Core.vhd.

◆ srpRdSlave

|

Port |

Definition at line 74 of file SrpV3Core.vhd.

◆ ieee

|

Library |

Definition at line 24 of file SrpV3Core.vhd.

◆ std_logic_1164

|

Package |

Definition at line 25 of file SrpV3Core.vhd.

◆ std_logic_arith

|

Package |

Definition at line 26 of file SrpV3Core.vhd.

◆ std_logic_unsigned

|

Package |

Definition at line 27 of file SrpV3Core.vhd.

◆ StdRtlPkg

|

Package |

Definition at line 29 of file SrpV3Core.vhd.

◆ AxiStreamPkg

|

Package |

Definition at line 30 of file SrpV3Core.vhd.

◆ SsiPkg

|

Package |

Definition at line 31 of file SrpV3Core.vhd.

◆ AxiLitePkg

|

Package |

Definition at line 32 of file SrpV3Core.vhd.

◆ SrpV3Pkg

|

Package |

Definition at line 33 of file SrpV3Core.vhd.

The documentation for this class was generated from the following file:

- protocols/srp/rtl/SrpV3Core.vhd