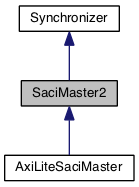

Inheritance diagram for SaciMaster2:

Inheritance diagram for SaciMaster2: Collaboration diagram for SaciMaster2:

Collaboration diagram for SaciMaster2:Entities | |

| rtl | architecture |

Libraries | |

| IEEE | |

Use Clauses | |

| std_logic_1164 | |

| std_logic_unsigned | |

| std_logic_arith | |

| StdRtlPkg | Package <StdRtlPkg> |

Generics | |

| TPD_G | time := 1 ns |

| SYS_CLK_PERIOD_G | real := 8 . 0e - 9 |

| SACI_CLK_PERIOD_G | real := 1 . 0e - 6 |

| SACI_CLK_FREERUN_G | boolean := false |

| SACI_NUM_CHIPS_G | positive := 1 |

| SACI_RSP_BUSSED_G | boolean := false |

Ports | |

| sysClk | in sl |

| sysRst | in sl |

| req | in sl |

| ack | out sl |

| fail | out sl |

| chip | in slv ( log2 ( SACI_NUM_CHIPS_G ) - 1 downto 0 ) |

| op | in sl |

| cmd | in slv ( 6 downto 0 ) |

| addr | in slv ( 11 downto 0 ) |

| wrData | in slv ( 31 downto 0 ) |

| rdData | out slv ( 31 downto 0 ) |

| saciClk | out sl |

| saciSelL | out slv ( SACI_NUM_CHIPS_G - 1 downto 0 ) |

| saciCmd | out sl |

| saciRsp | in slv ( ite ( SACI_RSP_BUSSED_G , 0 , SACI_NUM_CHIPS_G - 1 ) downto 0 ) |

Detailed Description

- See also

- entity

Definition at line 27 of file SaciMaster2.vhd.

Member Data Documentation

◆ TPD_G

|

Generic |

Definition at line 30 of file SaciMaster2.vhd.

◆ SYS_CLK_PERIOD_G

|

Generic |

Definition at line 31 of file SaciMaster2.vhd.

◆ SACI_CLK_PERIOD_G

|

Generic |

Definition at line 32 of file SaciMaster2.vhd.

◆ SACI_CLK_FREERUN_G

|

Generic |

Definition at line 33 of file SaciMaster2.vhd.

◆ SACI_NUM_CHIPS_G

|

Generic |

Definition at line 34 of file SaciMaster2.vhd.

◆ SACI_RSP_BUSSED_G

|

Generic |

Definition at line 35 of file SaciMaster2.vhd.

◆ sysClk

Definition at line 37 of file SaciMaster2.vhd.

◆ sysRst

Definition at line 38 of file SaciMaster2.vhd.

◆ req

Definition at line 41 of file SaciMaster2.vhd.

◆ ack

Definition at line 42 of file SaciMaster2.vhd.

◆ fail

Definition at line 43 of file SaciMaster2.vhd.

◆ chip

|

Port |

Definition at line 44 of file SaciMaster2.vhd.

◆ op

Definition at line 45 of file SaciMaster2.vhd.

◆ cmd

Definition at line 46 of file SaciMaster2.vhd.

◆ addr

Definition at line 47 of file SaciMaster2.vhd.

◆ wrData

Definition at line 48 of file SaciMaster2.vhd.

◆ rdData

Definition at line 49 of file SaciMaster2.vhd.

◆ saciClk

Definition at line 52 of file SaciMaster2.vhd.

◆ saciSelL

|

Port |

Definition at line 53 of file SaciMaster2.vhd.

◆ saciCmd

Definition at line 54 of file SaciMaster2.vhd.

◆ saciRsp

|

Port |

Definition at line 55 of file SaciMaster2.vhd.

◆ IEEE

|

Library |

Definition at line 18 of file SaciMaster2.vhd.

◆ std_logic_1164

|

Package |

Definition at line 19 of file SaciMaster2.vhd.

◆ std_logic_unsigned

|

Package |

Definition at line 20 of file SaciMaster2.vhd.

◆ std_logic_arith

|

Package |

Definition at line 21 of file SaciMaster2.vhd.

◆ StdRtlPkg

|

Package |

Definition at line 23 of file SaciMaster2.vhd.

The documentation for this class was generated from the following file:

- protocols/saci/rtl/SaciMaster2.vhd