Inheritance diagram for RssiCoreWrapper:

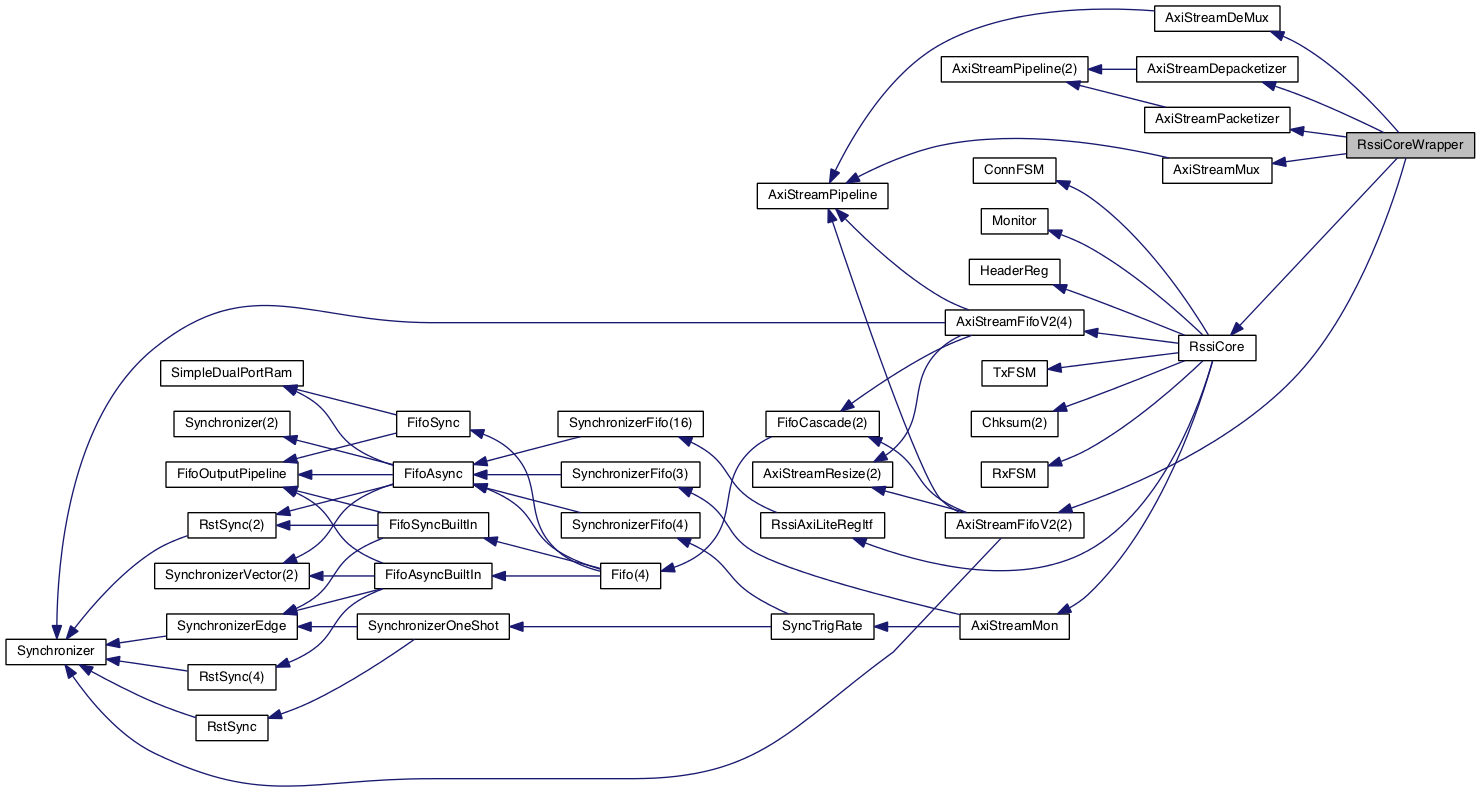

Inheritance diagram for RssiCoreWrapper: Collaboration diagram for RssiCoreWrapper:

Collaboration diagram for RssiCoreWrapper:Entities | |

| mapping | architecture |

Libraries | |

| ieee | |

Use Clauses | |

| std_logic_1164 | |

| StdRtlPkg | Package <StdRtlPkg> |

| RssiPkg | Package <RssiPkg> |

| SsiPkg | Package <SsiPkg> |

| AxiStreamPkg | Package <AxiStreamPkg> |

| AxiLitePkg | Package <AxiLitePkg> |

Generics | |

| TPD_G | time := 1 ns |

| CLK_FREQUENCY_G | real := 100 . 0E + 6 |

| TIMEOUT_UNIT_G | real := 1 . 0E - 6 |

| SERVER_G | boolean := true |

| RETRANSMIT_ENABLE_G | boolean := true |

| WINDOW_ADDR_SIZE_G | positive := 3 |

| SEGMENT_ADDR_SIZE_G | positive := 7 |

| BYPASS_CHUNKER_G | boolean := false |

| PIPE_STAGES_G | natural := 0 |

| APP_STREAMS_G | positive := 1 |

| APP_STREAM_ROUTES_G | Slv8Array := ( 0 = > " -------- " ) |

| AXI_ERROR_RESP_G | slv ( 1 downto 0 ) := AXI_RESP_DECERR_C |

| APP_AXIS_CONFIG_G | AxiStreamConfigArray := ( 0 = > ssiAxiStreamConfig ( 8 , TKEEP_NORMAL_C ) ) |

| TSP_AXIS_CONFIG_G | AxiStreamConfigType := ssiAxiStreamConfig ( 16 , TKEEP_NORMAL_C ) |

| INIT_SEQ_N_G | natural := 16#80# |

| CONN_ID_G | positive := 16#12345678# |

| VERSION_G | positive := 1 |

| HEADER_CHKSUM_EN_G | boolean := true |

| MAX_NUM_OUTS_SEG_G | positive := 8 |

| MAX_SEG_SIZE_G | positive := 1024 |

| ACK_TOUT_G | positive := 25 |

| RETRANS_TOUT_G | positive := 50 |

| NULL_TOUT_G | positive := 200 |

| MAX_RETRANS_CNT_G | positive := 2 |

| MAX_CUM_ACK_CNT_G | positive := 3 |

Ports | |

| clk_i | in sl |

| rst_i | in sl |

| sAppAxisMasters_i | in AxiStreamMasterArray ( APP_STREAMS_G - 1 downto 0 ) |

| sAppAxisSlaves_o | out AxiStreamSlaveArray ( APP_STREAMS_G - 1 downto 0 ) |

| mAppAxisMasters_o | out AxiStreamMasterArray ( APP_STREAMS_G - 1 downto 0 ) |

| mAppAxisSlaves_i | in AxiStreamSlaveArray ( APP_STREAMS_G - 1 downto 0 ) |

| sTspAxisMaster_i | in AxiStreamMasterType |

| sTspAxisSlave_o | out AxiStreamSlaveType |

| mTspAxisMaster_o | out AxiStreamMasterType |

| mTspAxisSlave_i | in AxiStreamSlaveType |

| openRq_i | in sl := ' 0 ' |

| closeRq_i | in sl := ' 0 ' |

| inject_i | in sl := ' 0 ' |

| axiClk_i | in sl := ' 0 ' |

| axiRst_i | in sl := ' 0 ' |

| axilReadMaster | in AxiLiteReadMasterType := AXI_LITE_READ_MASTER_INIT_C |

| axilReadSlave | out AxiLiteReadSlaveType |

| axilWriteMaster | in AxiLiteWriteMasterType := AXI_LITE_WRITE_MASTER_INIT_C |

| axilWriteSlave | out AxiLiteWriteSlaveType |

| statusReg_o | out slv ( 6 downto 0 ) |

Detailed Description

- See also

- entity

Definition at line 29 of file RssiCoreWrapper.vhd.

Member Data Documentation

◆ TPD_G

|

Generic |

Definition at line 31 of file RssiCoreWrapper.vhd.

◆ CLK_FREQUENCY_G

|

Generic |

Definition at line 32 of file RssiCoreWrapper.vhd.

◆ TIMEOUT_UNIT_G

|

Generic |

Definition at line 33 of file RssiCoreWrapper.vhd.

◆ SERVER_G

|

Generic |

Definition at line 34 of file RssiCoreWrapper.vhd.

◆ RETRANSMIT_ENABLE_G

|

Generic |

Definition at line 35 of file RssiCoreWrapper.vhd.

◆ WINDOW_ADDR_SIZE_G

|

Generic |

Definition at line 36 of file RssiCoreWrapper.vhd.

◆ SEGMENT_ADDR_SIZE_G

|

Generic |

Definition at line 37 of file RssiCoreWrapper.vhd.

◆ BYPASS_CHUNKER_G

|

Generic |

Definition at line 38 of file RssiCoreWrapper.vhd.

◆ PIPE_STAGES_G

|

Generic |

Definition at line 39 of file RssiCoreWrapper.vhd.

◆ APP_STREAMS_G

|

Generic |

Definition at line 40 of file RssiCoreWrapper.vhd.

◆ APP_STREAM_ROUTES_G

|

Generic |

Definition at line 41 of file RssiCoreWrapper.vhd.

◆ AXI_ERROR_RESP_G

|

Generic |

Definition at line 42 of file RssiCoreWrapper.vhd.

◆ APP_AXIS_CONFIG_G

|

Generic |

Definition at line 44 of file RssiCoreWrapper.vhd.

◆ TSP_AXIS_CONFIG_G

|

Generic |

Definition at line 45 of file RssiCoreWrapper.vhd.

◆ INIT_SEQ_N_G

|

Generic |

Definition at line 47 of file RssiCoreWrapper.vhd.

◆ CONN_ID_G

|

Generic |

Definition at line 48 of file RssiCoreWrapper.vhd.

◆ VERSION_G

|

Generic |

Definition at line 49 of file RssiCoreWrapper.vhd.

◆ HEADER_CHKSUM_EN_G

|

Generic |

Definition at line 50 of file RssiCoreWrapper.vhd.

◆ MAX_NUM_OUTS_SEG_G

|

Generic |

Definition at line 52 of file RssiCoreWrapper.vhd.

◆ MAX_SEG_SIZE_G

|

Generic |

Definition at line 53 of file RssiCoreWrapper.vhd.

◆ ACK_TOUT_G

|

Generic |

Definition at line 55 of file RssiCoreWrapper.vhd.

◆ RETRANS_TOUT_G

|

Generic |

Definition at line 56 of file RssiCoreWrapper.vhd.

◆ NULL_TOUT_G

|

Generic |

Definition at line 57 of file RssiCoreWrapper.vhd.

◆ MAX_RETRANS_CNT_G

|

Generic |

Definition at line 59 of file RssiCoreWrapper.vhd.

◆ MAX_CUM_ACK_CNT_G

|

Generic |

Definition at line 60 of file RssiCoreWrapper.vhd.

◆ clk_i

Definition at line 63 of file RssiCoreWrapper.vhd.

◆ rst_i

Definition at line 64 of file RssiCoreWrapper.vhd.

◆ sAppAxisMasters_i

|

Port |

Definition at line 66 of file RssiCoreWrapper.vhd.

◆ sAppAxisSlaves_o

|

Port |

Definition at line 67 of file RssiCoreWrapper.vhd.

◆ mAppAxisMasters_o

|

Port |

Definition at line 68 of file RssiCoreWrapper.vhd.

◆ mAppAxisSlaves_i

|

Port |

Definition at line 69 of file RssiCoreWrapper.vhd.

◆ sTspAxisMaster_i

|

Port |

Definition at line 71 of file RssiCoreWrapper.vhd.

◆ sTspAxisSlave_o

|

Port |

Definition at line 72 of file RssiCoreWrapper.vhd.

◆ mTspAxisMaster_o

|

Port |

Definition at line 73 of file RssiCoreWrapper.vhd.

◆ mTspAxisSlave_i

|

Port |

Definition at line 74 of file RssiCoreWrapper.vhd.

◆ openRq_i

Definition at line 76 of file RssiCoreWrapper.vhd.

◆ closeRq_i

Definition at line 77 of file RssiCoreWrapper.vhd.

◆ inject_i

Definition at line 78 of file RssiCoreWrapper.vhd.

◆ axiClk_i

Definition at line 80 of file RssiCoreWrapper.vhd.

◆ axiRst_i

Definition at line 81 of file RssiCoreWrapper.vhd.

◆ axilReadMaster

Definition at line 82 of file RssiCoreWrapper.vhd.

◆ axilReadSlave

|

Port |

Definition at line 83 of file RssiCoreWrapper.vhd.

◆ axilWriteMaster

Definition at line 84 of file RssiCoreWrapper.vhd.

◆ axilWriteSlave

|

Port |

Definition at line 85 of file RssiCoreWrapper.vhd.

◆ statusReg_o

|

Port |

Definition at line 87 of file RssiCoreWrapper.vhd.

◆ ieee

|

Library |

Definition at line 18 of file RssiCoreWrapper.vhd.

◆ std_logic_1164

|

Package |

Definition at line 19 of file RssiCoreWrapper.vhd.

◆ StdRtlPkg

|

Package |

Definition at line 21 of file RssiCoreWrapper.vhd.

◆ RssiPkg

|

Package |

Definition at line 22 of file RssiCoreWrapper.vhd.

◆ SsiPkg

|

Package |

Definition at line 23 of file RssiCoreWrapper.vhd.

◆ AxiStreamPkg

|

Package |

Definition at line 24 of file RssiCoreWrapper.vhd.

◆ AxiLitePkg

|

Package |

Definition at line 25 of file RssiCoreWrapper.vhd.

The documentation for this class was generated from the following file:

- protocols/rssi/rtl/RssiCoreWrapper.vhd