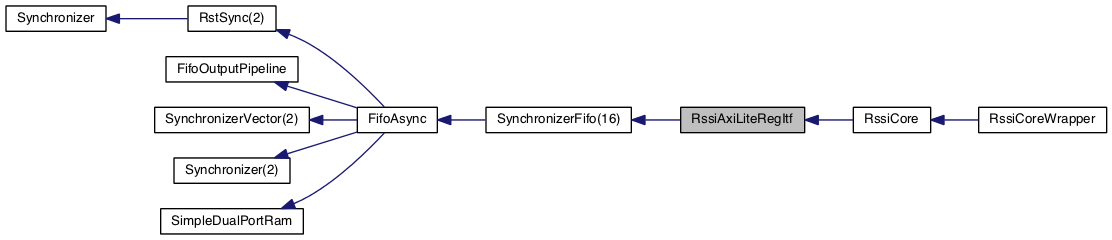

Inheritance diagram for RssiAxiLiteRegItf:

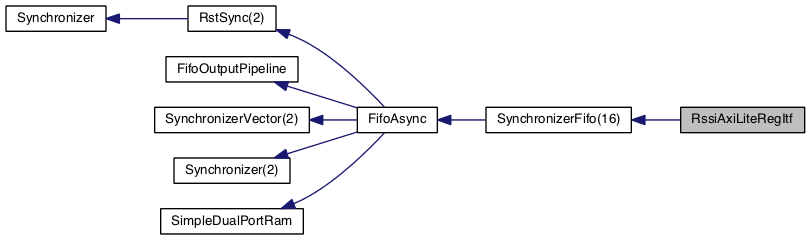

Inheritance diagram for RssiAxiLiteRegItf: Collaboration diagram for RssiAxiLiteRegItf:

Collaboration diagram for RssiAxiLiteRegItf:Entities | |

| rtl | architecture |

Libraries | |

| ieee | |

Use Clauses | |

| std_logic_1164 | |

| std_logic_unsigned | |

| std_logic_arith | |

| StdRtlPkg | Package <StdRtlPkg> |

| AxiLitePkg | Package <AxiLitePkg> |

| RssiPkg | Package <RssiPkg> |

Generics | |

| TPD_G | time := 1 ns |

| AXI_ERROR_RESP_G | slv ( 1 downto 0 ) := AXI_RESP_SLVERR_C |

| SEGMENT_ADDR_SIZE_G | positive := 3 |

| TIMEOUT_UNIT_G | real := 1 . 0E - 6 |

| INIT_SEQ_N_G | natural := 16#80# |

| CONN_ID_G | positive := 16#12345678# |

| VERSION_G | positive := 1 |

| HEADER_CHKSUM_EN_G | boolean := true |

| MAX_NUM_OUTS_SEG_G | positive := 8 |

| MAX_SEG_SIZE_G | positive := 1024 |

| RETRANS_TOUT_G | positive := 50 |

| ACK_TOUT_G | positive := 25 |

| NULL_TOUT_G | positive := 200 |

| MAX_RETRANS_CNT_G | positive := 2 |

| MAX_CUM_ACK_CNT_G | positive := 3 |

| MAX_OUT_OF_SEQUENCE_G | natural := 3 |

Ports | |

| axiClk_i | in sl |

| axiRst_i | in sl |

| axilReadMaster | in AxiLiteReadMasterType := AXI_LITE_READ_MASTER_INIT_C |

| axilReadSlave | out AxiLiteReadSlaveType |

| axilWriteMaster | in AxiLiteWriteMasterType := AXI_LITE_WRITE_MASTER_INIT_C |

| axilWriteSlave | out AxiLiteWriteSlaveType |

| devClk_i | in sl |

| devRst_i | in sl |

| openRq_o | out sl |

| closeRq_o | out sl |

| mode_o | out sl |

| injectFault_o | out sl |

| initSeqN_o | out slv ( 7 downto 0 ) |

| appRssiParam_o | out RssiParamType |

| frameRate_i | in Slv32Array ( 1 downto 0 ) |

| bandwidth_i | in Slv64Array ( 1 downto 0 ) |

| status_i | in slv ( 6 downto 0 ) |

| dropCnt_i | in slv ( 31 downto 0 ) |

| validCnt_i | in slv ( 31 downto 0 ) |

| resendCnt_i | in slv ( 31 downto 0 ) |

| reconCnt_i | in slv ( 31 downto 0 ) |

Detailed Description

- See also

- entity

Definition at line 79 of file RssiAxiLiteRegItf.vhd.

Member Data Documentation

◆ TPD_G

|

Generic |

Definition at line 82 of file RssiAxiLiteRegItf.vhd.

◆ AXI_ERROR_RESP_G

|

Generic |

Definition at line 83 of file RssiAxiLiteRegItf.vhd.

◆ SEGMENT_ADDR_SIZE_G

|

Generic |

Definition at line 84 of file RssiAxiLiteRegItf.vhd.

◆ TIMEOUT_UNIT_G

|

Generic |

Definition at line 86 of file RssiAxiLiteRegItf.vhd.

◆ INIT_SEQ_N_G

|

Generic |

Definition at line 87 of file RssiAxiLiteRegItf.vhd.

◆ CONN_ID_G

|

Generic |

Definition at line 88 of file RssiAxiLiteRegItf.vhd.

◆ VERSION_G

|

Generic |

Definition at line 89 of file RssiAxiLiteRegItf.vhd.

◆ HEADER_CHKSUM_EN_G

|

Generic |

Definition at line 90 of file RssiAxiLiteRegItf.vhd.

◆ MAX_NUM_OUTS_SEG_G

|

Generic |

Definition at line 91 of file RssiAxiLiteRegItf.vhd.

◆ MAX_SEG_SIZE_G

|

Generic |

Definition at line 92 of file RssiAxiLiteRegItf.vhd.

◆ RETRANS_TOUT_G

|

Generic |

Definition at line 93 of file RssiAxiLiteRegItf.vhd.

◆ ACK_TOUT_G

|

Generic |

Definition at line 94 of file RssiAxiLiteRegItf.vhd.

◆ NULL_TOUT_G

|

Generic |

Definition at line 95 of file RssiAxiLiteRegItf.vhd.

◆ MAX_RETRANS_CNT_G

|

Generic |

Definition at line 96 of file RssiAxiLiteRegItf.vhd.

◆ MAX_CUM_ACK_CNT_G

|

Generic |

Definition at line 97 of file RssiAxiLiteRegItf.vhd.

◆ MAX_OUT_OF_SEQUENCE_G

|

Generic |

Definition at line 98 of file RssiAxiLiteRegItf.vhd.

◆ axiClk_i

Definition at line 102 of file RssiAxiLiteRegItf.vhd.

◆ axiRst_i

Definition at line 103 of file RssiAxiLiteRegItf.vhd.

◆ axilReadMaster

Definition at line 106 of file RssiAxiLiteRegItf.vhd.

◆ axilReadSlave

|

Port |

Definition at line 107 of file RssiAxiLiteRegItf.vhd.

◆ axilWriteMaster

Definition at line 108 of file RssiAxiLiteRegItf.vhd.

◆ axilWriteSlave

|

Port |

Definition at line 109 of file RssiAxiLiteRegItf.vhd.

◆ devClk_i

Definition at line 112 of file RssiAxiLiteRegItf.vhd.

◆ devRst_i

Definition at line 113 of file RssiAxiLiteRegItf.vhd.

◆ openRq_o

Definition at line 117 of file RssiAxiLiteRegItf.vhd.

◆ closeRq_o

Definition at line 118 of file RssiAxiLiteRegItf.vhd.

◆ mode_o

Definition at line 119 of file RssiAxiLiteRegItf.vhd.

◆ injectFault_o

|

Port |

Definition at line 120 of file RssiAxiLiteRegItf.vhd.

◆ initSeqN_o

|

Port |

Definition at line 122 of file RssiAxiLiteRegItf.vhd.

◆ appRssiParam_o

|

Port |

Definition at line 123 of file RssiAxiLiteRegItf.vhd.

◆ frameRate_i

|

Port |

Definition at line 126 of file RssiAxiLiteRegItf.vhd.

◆ bandwidth_i

|

Port |

Definition at line 127 of file RssiAxiLiteRegItf.vhd.

◆ status_i

Definition at line 128 of file RssiAxiLiteRegItf.vhd.

◆ dropCnt_i

Definition at line 129 of file RssiAxiLiteRegItf.vhd.

◆ validCnt_i

|

Port |

Definition at line 130 of file RssiAxiLiteRegItf.vhd.

◆ resendCnt_i

|

Port |

Definition at line 131 of file RssiAxiLiteRegItf.vhd.

◆ reconCnt_i

|

Port |

Definition at line 133 of file RssiAxiLiteRegItf.vhd.

◆ ieee

|

Library |

Definition at line 68 of file RssiAxiLiteRegItf.vhd.

◆ std_logic_1164

|

Package |

Definition at line 69 of file RssiAxiLiteRegItf.vhd.

◆ std_logic_unsigned

|

Package |

Definition at line 70 of file RssiAxiLiteRegItf.vhd.

◆ std_logic_arith

|

Package |

Definition at line 71 of file RssiAxiLiteRegItf.vhd.

◆ StdRtlPkg

|

Package |

Definition at line 73 of file RssiAxiLiteRegItf.vhd.

◆ AxiLitePkg

|

Package |

Definition at line 74 of file RssiAxiLiteRegItf.vhd.

◆ RssiPkg

|

Package |

Definition at line 75 of file RssiAxiLiteRegItf.vhd.

The documentation for this class was generated from the following file:

- protocols/rssi/rtl/RssiAxiLiteRegItf.vhd