Inheritance diagram for Pgp2bLane:

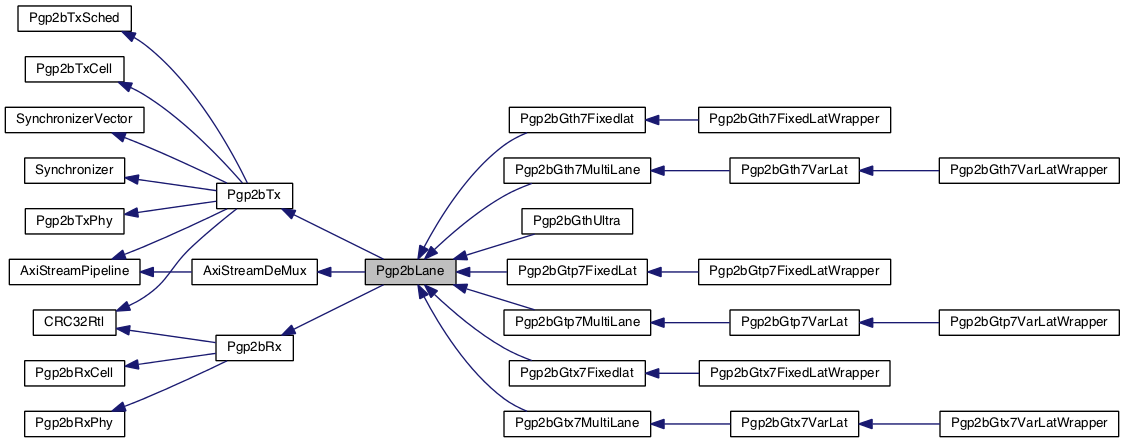

Inheritance diagram for Pgp2bLane: Collaboration diagram for Pgp2bLane:

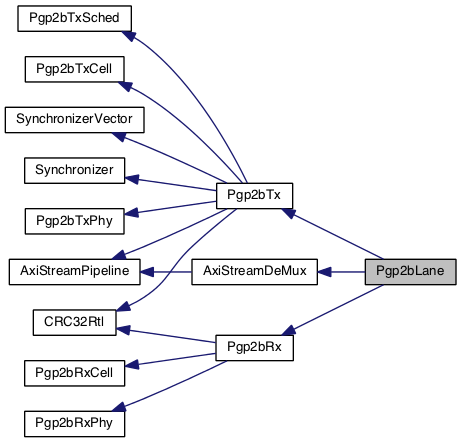

Collaboration diagram for Pgp2bLane:Entities | |

| Pgp2bLane | architecture |

Libraries | |

| ieee | |

Use Clauses | |

| std_logic_1164 | |

| std_logic_arith | |

| std_logic_unsigned | |

| StdRtlPkg | Package <StdRtlPkg> |

| Pgp2bPkg | Package <Pgp2bPkg> |

| AxiStreamPkg | Package <AxiStreamPkg> |

| SsiPkg | Package <SsiPkg> |

Generics | |

| TPD_G | time := 1 ns |

| LANE_CNT_G | integer range 1 to 2 := 1 |

| VC_INTERLEAVE_G | integer := 1 |

| PAYLOAD_CNT_TOP_G | integer := 7 |

| NUM_VC_EN_G | integer range 1 to 4 := 4 |

| TX_ENABLE_G | boolean := true |

| RX_ENABLE_G | boolean := true |

Ports | |

| pgpTxClkEn | in sl := ' 1 ' |

| pgpTxClk | in sl := ' 0 ' |

| pgpTxClkRst | in sl := ' 0 ' |

| pgpTxIn | in Pgp2bTxInType := PGP2B_TX_IN_INIT_C |

| pgpTxOut | out Pgp2bTxOutType |

| pgpTxMasters | in AxiStreamMasterArray ( 3 downto 0 ) := ( others = > AXI_STREAM_MASTER_INIT_C ) |

| pgpTxSlaves | out AxiStreamSlaveArray ( 3 downto 0 ) |

| phyTxLanesOut | out Pgp2bTxPhyLaneOutArray ( 0 to LANE_CNT_G - 1 ) |

| phyTxReady | in sl := ' 0 ' |

| pgpRxClkEn | in sl := ' 1 ' |

| pgpRxClk | in sl := ' 0 ' |

| pgpRxClkRst | in sl := ' 0 ' |

| pgpRxIn | in Pgp2bRxInType := PGP2B_RX_IN_INIT_C |

| pgpRxOut | out Pgp2bRxOutType |

| pgpRxMasters | out AxiStreamMasterArray ( 3 downto 0 ) |

| pgpRxMasterMuxed | out AxiStreamMasterType |

| pgpRxCtrl | in AxiStreamCtrlArray ( 3 downto 0 ) := ( others = > AXI_STREAM_CTRL_UNUSED_C ) |

| phyRxLanesOut | out Pgp2bRxPhyLaneOutArray ( 0 to LANE_CNT_G - 1 ) |

| phyRxLanesIn | in Pgp2bRxPhyLaneInArray ( 0 to LANE_CNT_G - 1 ) := ( others = > PGP2B_RX_PHY_LANE_IN_INIT_C ) |

| phyRxReady | in sl := ' 0 ' |

| phyRxInit | out sl |

Detailed Description

- See also

- entity

Definition at line 31 of file Pgp2bLane.vhd.

Member Data Documentation

◆ TPD_G

|

Generic |

Definition at line 33 of file Pgp2bLane.vhd.

◆ LANE_CNT_G

|

Generic |

Definition at line 34 of file Pgp2bLane.vhd.

◆ VC_INTERLEAVE_G

|

Generic |

Definition at line 35 of file Pgp2bLane.vhd.

◆ PAYLOAD_CNT_TOP_G

|

Generic |

Definition at line 36 of file Pgp2bLane.vhd.

◆ NUM_VC_EN_G

|

Generic |

Definition at line 37 of file Pgp2bLane.vhd.

◆ TX_ENABLE_G

|

Generic |

Definition at line 38 of file Pgp2bLane.vhd.

◆ RX_ENABLE_G

|

Generic |

Definition at line 40 of file Pgp2bLane.vhd.

◆ pgpTxClkEn

|

Port |

Definition at line 48 of file Pgp2bLane.vhd.

◆ pgpTxClk

Definition at line 49 of file Pgp2bLane.vhd.

◆ pgpTxClkRst

|

Port |

Definition at line 50 of file Pgp2bLane.vhd.

◆ pgpTxIn

|

Port |

Definition at line 53 of file Pgp2bLane.vhd.

◆ pgpTxOut

|

Port |

Definition at line 54 of file Pgp2bLane.vhd.

◆ pgpTxMasters

|

Port |

Definition at line 57 of file Pgp2bLane.vhd.

◆ pgpTxSlaves

|

Port |

Definition at line 58 of file Pgp2bLane.vhd.

◆ phyTxLanesOut

|

Port |

Definition at line 61 of file Pgp2bLane.vhd.

◆ phyTxReady

|

Port |

Definition at line 62 of file Pgp2bLane.vhd.

◆ pgpRxClkEn

|

Port |

Definition at line 69 of file Pgp2bLane.vhd.

◆ pgpRxClk

Definition at line 70 of file Pgp2bLane.vhd.

◆ pgpRxClkRst

|

Port |

Definition at line 71 of file Pgp2bLane.vhd.

◆ pgpRxIn

|

Port |

Definition at line 74 of file Pgp2bLane.vhd.

◆ pgpRxOut

|

Port |

Definition at line 75 of file Pgp2bLane.vhd.

◆ pgpRxMasters

|

Port |

Definition at line 78 of file Pgp2bLane.vhd.

◆ pgpRxMasterMuxed

|

Port |

Definition at line 79 of file Pgp2bLane.vhd.

◆ pgpRxCtrl

|

Port |

Definition at line 82 of file Pgp2bLane.vhd.

◆ phyRxLanesOut

|

Port |

Definition at line 85 of file Pgp2bLane.vhd.

◆ phyRxLanesIn

|

Port |

Definition at line 86 of file Pgp2bLane.vhd.

◆ phyRxReady

|

Port |

Definition at line 87 of file Pgp2bLane.vhd.

◆ phyRxInit

Definition at line 89 of file Pgp2bLane.vhd.

◆ ieee

|

Library |

Definition at line 19 of file Pgp2bLane.vhd.

◆ std_logic_1164

|

Package |

Definition at line 20 of file Pgp2bLane.vhd.

◆ std_logic_arith

|

Package |

Definition at line 21 of file Pgp2bLane.vhd.

◆ std_logic_unsigned

|

Package |

Definition at line 22 of file Pgp2bLane.vhd.

◆ StdRtlPkg

|

Package |

Definition at line 24 of file Pgp2bLane.vhd.

◆ Pgp2bPkg

|

Package |

Definition at line 25 of file Pgp2bLane.vhd.

◆ AxiStreamPkg

|

Package |

Definition at line 26 of file Pgp2bLane.vhd.

◆ SsiPkg

|

Package |

Definition at line 27 of file Pgp2bLane.vhd.

The documentation for this class was generated from the following file:

- protocols/pgp/pgp2b/core/rtl/Pgp2bLane.vhd