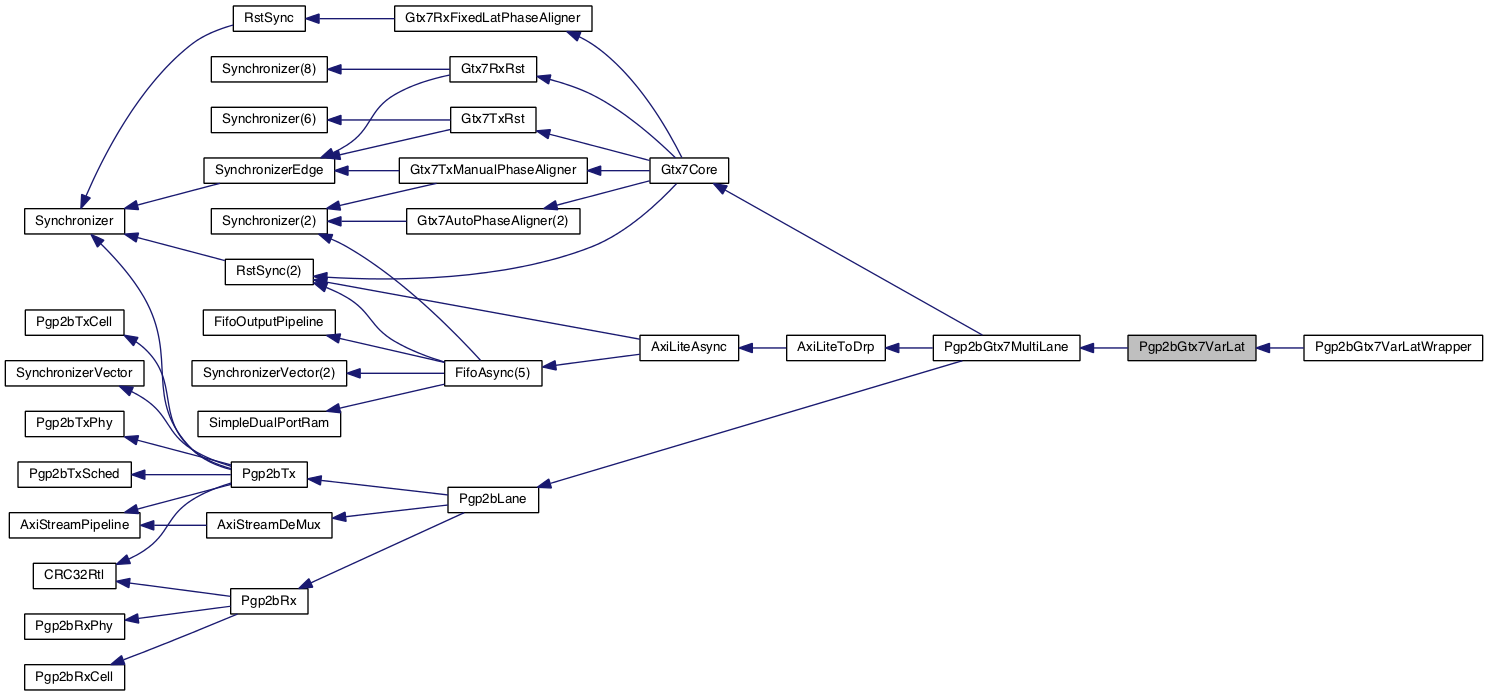

Inheritance diagram for Pgp2bGtx7VarLat:

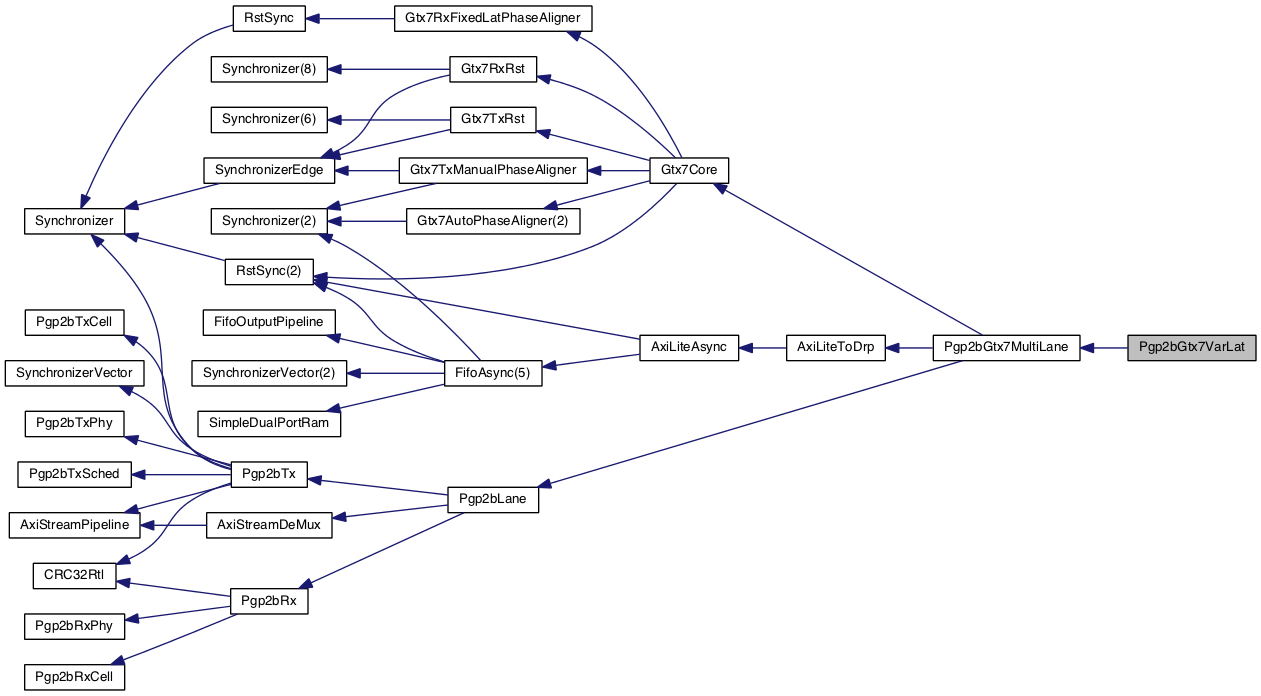

Inheritance diagram for Pgp2bGtx7VarLat: Collaboration diagram for Pgp2bGtx7VarLat:

Collaboration diagram for Pgp2bGtx7VarLat:Entities | |

| mapping | architecture |

Libraries | |

| ieee | |

Use Clauses | |

| std_logic_1164 | |

| StdRtlPkg | Package <StdRtlPkg> |

| AxiStreamPkg | Package <AxiStreamPkg> |

| Pgp2bPkg | Package <Pgp2bPkg> |

| AxiLitePkg | Package <AxiLitePkg> |

Generics | |

| TPD_G | time := 1 ns |

| SIM_GTRESET_SPEEDUP_G | string := " FALSE " |

| SIM_VERSION_G | string := " 4.0 " |

| STABLE_CLOCK_PERIOD_G | real := 4 . 0E - 9 |

| CPLL_REFCLK_SEL_G | bit_vector := " 001 " |

| CPLL_FBDIV_G | integer := 4 |

| CPLL_FBDIV_45_G | integer := 5 |

| CPLL_REFCLK_DIV_G | integer := 1 |

| RXOUT_DIV_G | integer := 2 |

| TXOUT_DIV_G | integer := 2 |

| RX_CLK25_DIV_G | integer := 7 |

| TX_CLK25_DIV_G | integer := 7 |

| PMA_RSV_G | bit_vector := x " 00018480 " |

| RX_OS_CFG_G | bit_vector := " 0000010000000 " |

| RXCDR_CFG_G | bit_vector := x " 03000023ff40200020 " |

| RXDFEXYDEN_G | sl := ' 0 ' |

| RX_DFE_KL_CFG2_G | bit_vector := x " 3010D90C " |

| TX_PLL_G | string := " QPLL " |

| RX_PLL_G | string := " CPLL " |

| TX_BUF_EN_G | boolean := true |

| TX_OUTCLK_SRC_G | string := " OUTCLKPMA " |

| TX_DLY_BYPASS_G | sl := ' 1 ' |

| TX_PHASE_ALIGN_G | string := " NONE " |

| TX_BUF_ADDR_MODE_G | string := " FULL " |

| VC_INTERLEAVE_G | integer := 0 |

| PAYLOAD_CNT_TOP_G | integer := 7 |

| NUM_VC_EN_G | integer range 1 to 4 := 4 |

| AXI_ERROR_RESP_G | slv ( 1 downto 0 ) := AXI_RESP_DECERR_C |

| TX_ENABLE_G | boolean := true |

| RX_ENABLE_G | boolean := true |

Detailed Description

- See also

- entity

Definition at line 28 of file Pgp2bGtx7VarLat.vhd.

Member Data Documentation

◆ TPD_G

|

Generic |

Definition at line 30 of file Pgp2bGtx7VarLat.vhd.

◆ SIM_GTRESET_SPEEDUP_G

|

Generic |

Definition at line 35 of file Pgp2bGtx7VarLat.vhd.

◆ SIM_VERSION_G

|

Generic |

Definition at line 36 of file Pgp2bGtx7VarLat.vhd.

◆ STABLE_CLOCK_PERIOD_G

|

Generic |

Definition at line 37 of file Pgp2bGtx7VarLat.vhd.

◆ CPLL_REFCLK_SEL_G

|

Generic |

Definition at line 39 of file Pgp2bGtx7VarLat.vhd.

◆ CPLL_FBDIV_G

|

Generic |

Definition at line 40 of file Pgp2bGtx7VarLat.vhd.

◆ CPLL_FBDIV_45_G

|

Generic |

Definition at line 41 of file Pgp2bGtx7VarLat.vhd.

◆ CPLL_REFCLK_DIV_G

|

Generic |

Definition at line 42 of file Pgp2bGtx7VarLat.vhd.

◆ RXOUT_DIV_G

|

Generic |

Definition at line 43 of file Pgp2bGtx7VarLat.vhd.

◆ TXOUT_DIV_G

|

Generic |

Definition at line 44 of file Pgp2bGtx7VarLat.vhd.

◆ RX_CLK25_DIV_G

|

Generic |

Definition at line 45 of file Pgp2bGtx7VarLat.vhd.

◆ TX_CLK25_DIV_G

|

Generic |

Definition at line 46 of file Pgp2bGtx7VarLat.vhd.

◆ PMA_RSV_G

|

Generic |

Definition at line 48 of file Pgp2bGtx7VarLat.vhd.

◆ RX_OS_CFG_G

|

Generic |

Definition at line 49 of file Pgp2bGtx7VarLat.vhd.

◆ RXCDR_CFG_G

|

Generic |

Definition at line 50 of file Pgp2bGtx7VarLat.vhd.

◆ RXDFEXYDEN_G

|

Generic |

Definition at line 51 of file Pgp2bGtx7VarLat.vhd.

◆ RX_DFE_KL_CFG2_G

|

Generic |

Definition at line 54 of file Pgp2bGtx7VarLat.vhd.

◆ TX_PLL_G

|

Generic |

Definition at line 56 of file Pgp2bGtx7VarLat.vhd.

◆ RX_PLL_G

|

Generic |

Definition at line 57 of file Pgp2bGtx7VarLat.vhd.

◆ TX_BUF_EN_G

|

Generic |

Definition at line 60 of file Pgp2bGtx7VarLat.vhd.

◆ TX_OUTCLK_SRC_G

|

Generic |

Definition at line 61 of file Pgp2bGtx7VarLat.vhd.

◆ TX_DLY_BYPASS_G

|

Generic |

Definition at line 62 of file Pgp2bGtx7VarLat.vhd.

◆ TX_PHASE_ALIGN_G

|

Generic |

Definition at line 63 of file Pgp2bGtx7VarLat.vhd.

◆ TX_BUF_ADDR_MODE_G

|

Generic |

Definition at line 64 of file Pgp2bGtx7VarLat.vhd.

◆ VC_INTERLEAVE_G

|

Generic |

Definition at line 69 of file Pgp2bGtx7VarLat.vhd.

◆ PAYLOAD_CNT_TOP_G

|

Generic |

Definition at line 70 of file Pgp2bGtx7VarLat.vhd.

◆ NUM_VC_EN_G

|

Generic |

Definition at line 71 of file Pgp2bGtx7VarLat.vhd.

◆ AXI_ERROR_RESP_G

|

Generic |

Definition at line 72 of file Pgp2bGtx7VarLat.vhd.

◆ TX_ENABLE_G

|

Generic |

Definition at line 73 of file Pgp2bGtx7VarLat.vhd.

◆ RX_ENABLE_G

|

Generic |

Definition at line 74 of file Pgp2bGtx7VarLat.vhd.

◆ stableClk

Definition at line 77 of file Pgp2bGtx7VarLat.vhd.

◆ gtCPllRefClk

|

Port |

Definition at line 78 of file Pgp2bGtx7VarLat.vhd.

◆ gtCPllLock

|

Port |

Definition at line 79 of file Pgp2bGtx7VarLat.vhd.

◆ gtQPllRefClk

|

Port |

Definition at line 80 of file Pgp2bGtx7VarLat.vhd.

◆ gtQPllClk

Definition at line 81 of file Pgp2bGtx7VarLat.vhd.

◆ gtQPllLock

|

Port |

Definition at line 82 of file Pgp2bGtx7VarLat.vhd.

◆ gtQPllRefClkLost

|

Port |

Definition at line 83 of file Pgp2bGtx7VarLat.vhd.

◆ gtQPllReset

|

Port |

Definition at line 84 of file Pgp2bGtx7VarLat.vhd.

◆ gtTxP

Definition at line 86 of file Pgp2bGtx7VarLat.vhd.

◆ gtTxN

Definition at line 87 of file Pgp2bGtx7VarLat.vhd.

◆ gtRxP

Definition at line 88 of file Pgp2bGtx7VarLat.vhd.

◆ gtRxN

Definition at line 89 of file Pgp2bGtx7VarLat.vhd.

◆ pgpTxReset

|

Port |

Definition at line 91 of file Pgp2bGtx7VarLat.vhd.

◆ pgpTxClk

Definition at line 92 of file Pgp2bGtx7VarLat.vhd.

◆ pgpTxRecClk

|

Port |

Definition at line 93 of file Pgp2bGtx7VarLat.vhd.

◆ pgpTxMmcmReset

|

Port |

Definition at line 94 of file Pgp2bGtx7VarLat.vhd.

◆ pgpTxMmcmLocked

|

Port |

Definition at line 95 of file Pgp2bGtx7VarLat.vhd.

◆ pgpRxReset

|

Port |

Definition at line 97 of file Pgp2bGtx7VarLat.vhd.

◆ pgpRxRecClk

|

Port |

Definition at line 98 of file Pgp2bGtx7VarLat.vhd.

◆ pgpRxClk

Definition at line 99 of file Pgp2bGtx7VarLat.vhd.

◆ pgpRxMmcmReset

|

Port |

Definition at line 100 of file Pgp2bGtx7VarLat.vhd.

◆ pgpRxMmcmLocked

|

Port |

Definition at line 101 of file Pgp2bGtx7VarLat.vhd.

◆ pgpRxIn

|

Port |

Definition at line 103 of file Pgp2bGtx7VarLat.vhd.

◆ pgpRxOut

|

Port |

Definition at line 104 of file Pgp2bGtx7VarLat.vhd.

◆ pgpTxIn

|

Port |

Definition at line 106 of file Pgp2bGtx7VarLat.vhd.

◆ pgpTxOut

|

Port |

Definition at line 107 of file Pgp2bGtx7VarLat.vhd.

◆ pgpTxMasters

|

Port |

Definition at line 109 of file Pgp2bGtx7VarLat.vhd.

◆ pgpTxSlaves

|

Port |

Definition at line 110 of file Pgp2bGtx7VarLat.vhd.

◆ pgpRxMasters

|

Port |

Definition at line 112 of file Pgp2bGtx7VarLat.vhd.

◆ pgpRxMasterMuxed

|

Port |

Definition at line 113 of file Pgp2bGtx7VarLat.vhd.

◆ pgpRxCtrl

|

Port |

Definition at line 114 of file Pgp2bGtx7VarLat.vhd.

◆ txPreCursor

|

Port |

Definition at line 116 of file Pgp2bGtx7VarLat.vhd.

◆ txPostCursor

|

Port |

Definition at line 117 of file Pgp2bGtx7VarLat.vhd.

◆ txDiffCtrl

|

Port |

Definition at line 118 of file Pgp2bGtx7VarLat.vhd.

◆ axilClk

Definition at line 120 of file Pgp2bGtx7VarLat.vhd.

◆ axilRst

Definition at line 121 of file Pgp2bGtx7VarLat.vhd.

◆ axilReadMaster

Definition at line 122 of file Pgp2bGtx7VarLat.vhd.

◆ axilReadSlave

|

Port |

Definition at line 123 of file Pgp2bGtx7VarLat.vhd.

◆ axilWriteMaster

Definition at line 124 of file Pgp2bGtx7VarLat.vhd.

◆ axilWriteSlave

|

Port |

Definition at line 125 of file Pgp2bGtx7VarLat.vhd.

◆ ieee

|

Library |

Definition at line 18 of file Pgp2bGtx7VarLat.vhd.

◆ std_logic_1164

|

Package |

Definition at line 19 of file Pgp2bGtx7VarLat.vhd.

◆ StdRtlPkg

|

Package |

Definition at line 21 of file Pgp2bGtx7VarLat.vhd.

◆ AxiStreamPkg

|

Package |

Definition at line 22 of file Pgp2bGtx7VarLat.vhd.

◆ Pgp2bPkg

|

Package |

Definition at line 23 of file Pgp2bGtx7VarLat.vhd.

◆ AxiLitePkg

|

Package |

Definition at line 24 of file Pgp2bGtx7VarLat.vhd.

The documentation for this class was generated from the following file:

- protocols/pgp/pgp2b/gtx7/rtl/Pgp2bGtx7VarLat.vhd