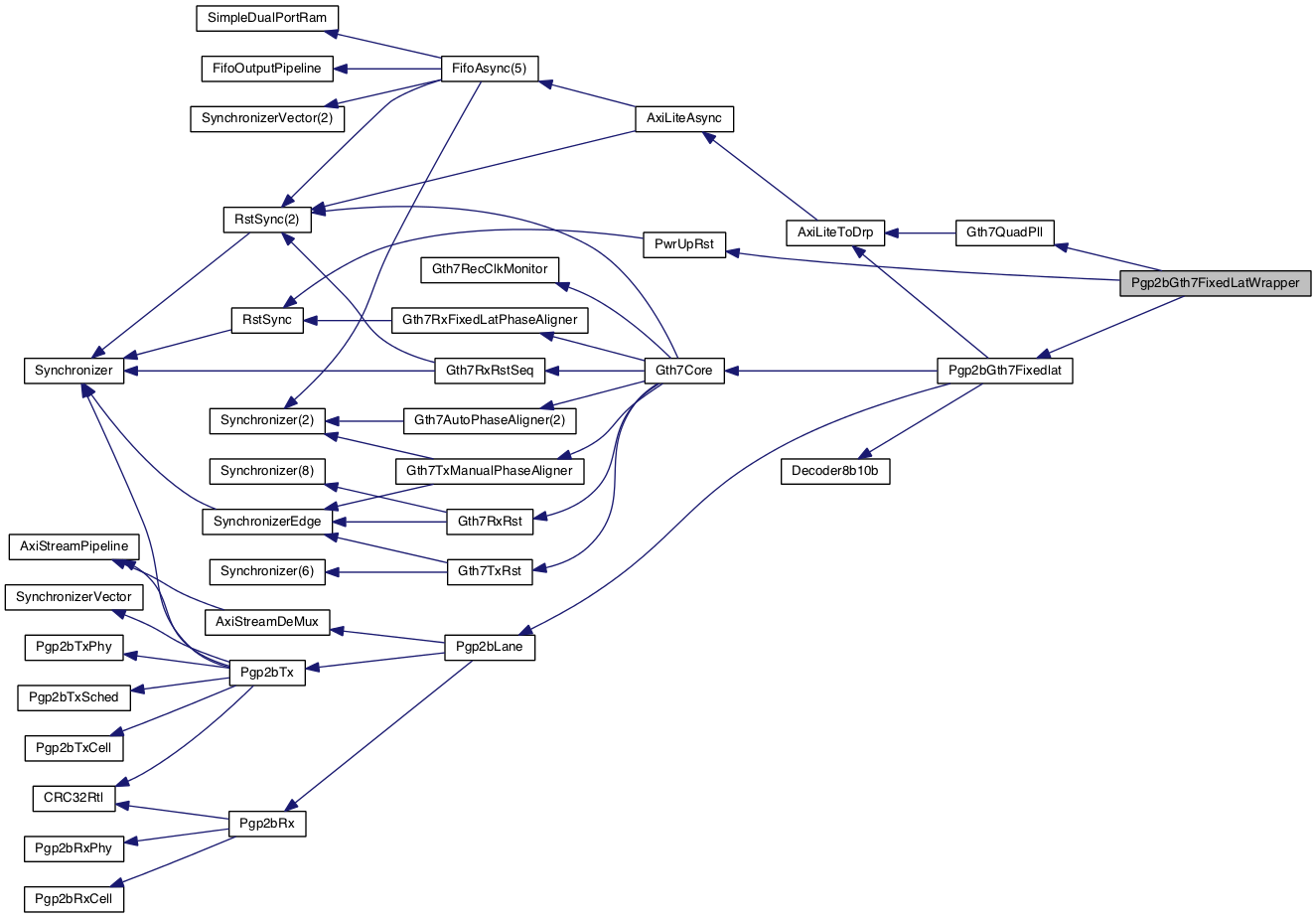

Inheritance diagram for Pgp2bGth7FixedLatWrapper:

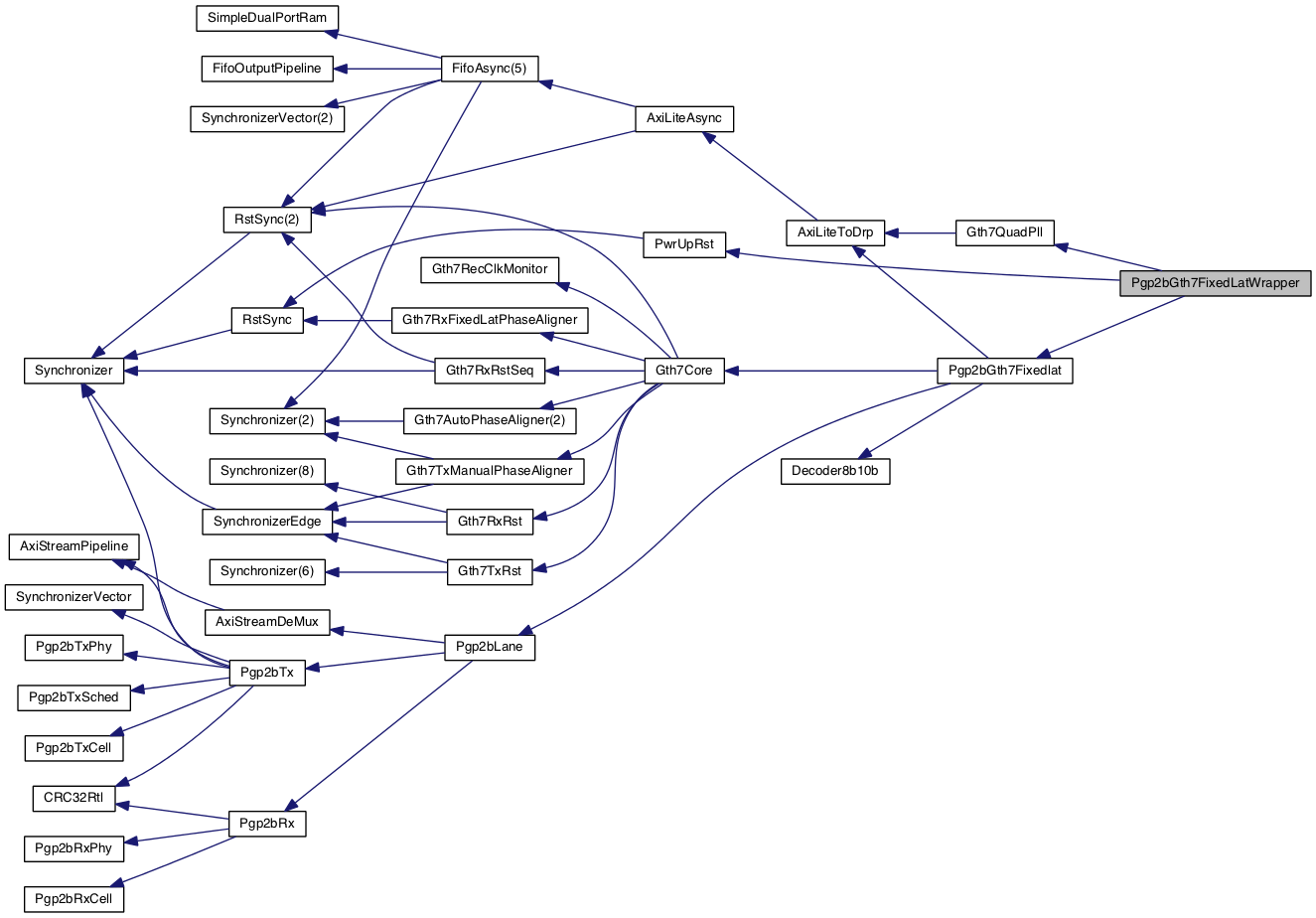

Inheritance diagram for Pgp2bGth7FixedLatWrapper: Collaboration diagram for Pgp2bGth7FixedLatWrapper:

Collaboration diagram for Pgp2bGth7FixedLatWrapper:Entities | |

| rtl | architecture |

Libraries | |

| ieee | |

| unisim | |

Use Clauses | |

| std_logic_1164 | |

| numeric_std | |

| StdRtlPkg | Package <StdRtlPkg> |

| AxiStreamPkg | Package <AxiStreamPkg> |

| Pgp2bPkg | Package <Pgp2bPkg> |

| AxiLitePkg | Package <AxiLitePkg> |

| vcomponents | |

Generics | |

| MASTER_SEL_G | boolean := true |

| RX_CLK_SEL_G | boolean := true |

| VC_INTERLEAVE_G | integer := 0 |

| PAYLOAD_CNT_TOP_G | integer := 7 |

| NUM_VC_EN_G | integer range 1 to 4 := 4 |

| AXI_ERROR_RESP_G | slv ( 1 downto 0 ) := AXI_RESP_DECERR_C |

| TX_ENABLE_G | boolean := true |

| RX_ENABLE_G | boolean := true |

| QPLL_FBDIV_G | bit_vector := " 0100100000 " |

| QPLL_FBDIV_RATIO_G | bit := ' 1 ' |

| QPLL_REFCLK_DIV_G | integer := 1 |

| CPLL_FBDIV_G | integer range 1 to 5 := 4 |

| CPLL_FBDIV_45_G | integer range 4 to 5 := 5 |

| CPLL_REFCLK_DIV_G | integer range 1 to 2 := 1 |

| MMCM_CLKIN_PERIOD_G | real := 8 . 000 |

| MMCM_CLKFBOUT_MULT_G | real := 8 . 000 |

| MMCM_GTCLK_DIVIDE_G | real := 8 . 000 |

| MMCM_TXCLK_DIVIDE_G | natural := 8 |

| RXOUT_DIV_G | integer := 2 |

| TXOUT_DIV_G | integer := 4 |

| RX_CLK25_DIV_G | integer := 5 |

| TX_CLK25_DIV_G | integer := 5 |

| RX_OS_CFG_G | bit_vector := " 0000010000000 " |

| RXCDR_CFG_G | bit_vector := x " 0002007FE1000C2200018 " |

| RXDFEXYDEN_G | sl := ' 0 ' |

| TX_PLL_G | string := " QPLL " |

| RX_PLL_G | string := " CPLL " |

Ports | |

| extRst | in sl |

| txPllLock | out sl |

| rxPllLock | out sl |

| txClk | out sl |

| rxClk | out sl |

| stableClk | out sl |

| pgpRxIn | in Pgp2bRxInType |

| pgpRxOut | out Pgp2bRxOutType |

| pgpTxIn | in Pgp2bTxInType |

| pgpTxOut | out Pgp2bTxOutType |

| pgpTxMasters | in AxiStreamMasterArray ( 3 downto 0 ) |

| pgpTxSlaves | out AxiStreamSlaveArray ( 3 downto 0 ) |

| pgpRxMasters | out AxiStreamMasterArray ( 3 downto 0 ) |

| pgpRxMasterMuxed | out AxiStreamMasterType |

| pgpRxCtrl | in AxiStreamCtrlArray ( 3 downto 0 ) |

| gtClkP | in sl |

| gtClkN | in sl |

| gtTxP | out sl |

| gtTxN | out sl |

| gtRxP | in sl |

| gtRxN | in sl |

| txPreCursor | in slv ( 4 downto 0 ) := ( others = > ' 0 ' ) |

| txPostCursor | in slv ( 4 downto 0 ) := ( others = > ' 0 ' ) |

| txDiffCtrl | in slv ( 3 downto 0 ) := " 1000 " |

| axilClk | in sl := ' 0 ' |

| axilRst | in sl := ' 0 ' |

| axilReadMaster | in AxiLiteReadMasterType := AXI_LITE_READ_MASTER_INIT_C |

| axilReadSlave | out AxiLiteReadSlaveType |

| axilWriteMaster | in AxiLiteWriteMasterType := AXI_LITE_WRITE_MASTER_INIT_C |

| axilWriteSlave | out AxiLiteWriteSlaveType |

Detailed Description

- See also

- entity

Definition at line 32 of file Pgp2bGth7FixedLatWrapper.vhd.

Member Data Documentation

◆ MASTER_SEL_G

|

Generic |

Definition at line 35 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ RX_CLK_SEL_G

|

Generic |

Definition at line 36 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ VC_INTERLEAVE_G

|

Generic |

Definition at line 38 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ PAYLOAD_CNT_TOP_G

|

Generic |

Definition at line 39 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ NUM_VC_EN_G

|

Generic |

Definition at line 40 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ AXI_ERROR_RESP_G

|

Generic |

Definition at line 41 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ TX_ENABLE_G

|

Generic |

Definition at line 42 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ RX_ENABLE_G

|

Generic |

Definition at line 43 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ QPLL_FBDIV_G

|

Generic |

Definition at line 45 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ QPLL_FBDIV_RATIO_G

|

Generic |

Definition at line 46 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ QPLL_REFCLK_DIV_G

|

Generic |

Definition at line 47 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ CPLL_FBDIV_G

|

Generic |

Definition at line 49 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ CPLL_FBDIV_45_G

|

Generic |

Definition at line 50 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ CPLL_REFCLK_DIV_G

|

Generic |

Definition at line 51 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ MMCM_CLKIN_PERIOD_G

|

Generic |

Definition at line 53 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ MMCM_CLKFBOUT_MULT_G

|

Generic |

Definition at line 54 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ MMCM_GTCLK_DIVIDE_G

|

Generic |

Definition at line 55 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ MMCM_TXCLK_DIVIDE_G

|

Generic |

Definition at line 56 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ RXOUT_DIV_G

|

Generic |

Definition at line 58 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ TXOUT_DIV_G

|

Generic |

Definition at line 59 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ RX_CLK25_DIV_G

|

Generic |

Definition at line 60 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ TX_CLK25_DIV_G

|

Generic |

Definition at line 61 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ RX_OS_CFG_G

|

Generic |

Definition at line 62 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ RXCDR_CFG_G

|

Generic |

Definition at line 63 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ RXDFEXYDEN_G

|

Generic |

Definition at line 64 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ TX_PLL_G

|

Generic |

Definition at line 65 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ RX_PLL_G

|

Generic |

Definition at line 66 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ extRst

Definition at line 69 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ txPllLock

Definition at line 71 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ rxPllLock

Definition at line 72 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ txClk

Definition at line 73 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ rxClk

Definition at line 74 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ stableClk

Definition at line 75 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ pgpRxIn

|

Port |

Definition at line 77 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ pgpRxOut

|

Port |

Definition at line 78 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ pgpTxIn

|

Port |

Definition at line 80 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ pgpTxOut

|

Port |

Definition at line 81 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ pgpTxMasters

|

Port |

Definition at line 83 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ pgpTxSlaves

|

Port |

Definition at line 84 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ pgpRxMasters

|

Port |

Definition at line 86 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ pgpRxMasterMuxed

|

Port |

Definition at line 87 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ pgpRxCtrl

|

Port |

Definition at line 88 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ gtClkP

Definition at line 90 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ gtClkN

Definition at line 91 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ gtTxP

Definition at line 92 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ gtTxN

Definition at line 93 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ gtRxP

Definition at line 94 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ gtRxN

Definition at line 95 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ txPreCursor

|

Port |

Definition at line 97 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ txPostCursor

|

Port |

Definition at line 98 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ txDiffCtrl

|

Port |

Definition at line 99 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ axilClk

Definition at line 101 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ axilRst

Definition at line 102 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ axilReadMaster

Definition at line 103 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ axilReadSlave

|

Port |

Definition at line 104 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ axilWriteMaster

Definition at line 105 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ axilWriteSlave

|

Port |

Definition at line 106 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ ieee

|

Library |

Definition at line 18 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ std_logic_1164

|

Package |

Definition at line 19 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ numeric_std

|

Package |

Definition at line 20 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ StdRtlPkg

|

Package |

Definition at line 22 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ AxiStreamPkg

|

Package |

Definition at line 23 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ Pgp2bPkg

|

Package |

Definition at line 24 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ AxiLitePkg

|

Package |

Definition at line 25 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ unisim

|

Library |

Definition at line 27 of file Pgp2bGth7FixedLatWrapper.vhd.

◆ vcomponents

|

Package |

Definition at line 28 of file Pgp2bGth7FixedLatWrapper.vhd.

The documentation for this class was generated from the following file:

- protocols/pgp/pgp2b/gth7/rtl/Pgp2bGth7FixedLatWrapper.vhd