Inheritance diagram for JesdTxLane:

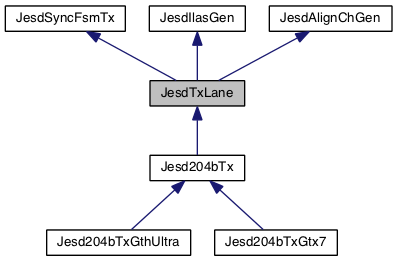

Inheritance diagram for JesdTxLane: Collaboration diagram for JesdTxLane:

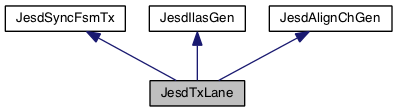

Collaboration diagram for JesdTxLane:Entities | |

| rtl | architecture |

Libraries | |

| ieee | |

Use Clauses | |

| std_logic_1164 | |

| std_logic_arith | |

| std_logic_unsigned | |

| StdRtlPkg | Package <StdRtlPkg> |

| Jesd204bPkg | Package <Jesd204bPkg> |

Generics | |

| TPD_G | time := 1 ns |

| F_G | positive := 2 |

| K_G | positive := 32 |

Ports | |

| devClk_i | in sl |

| devRst_i | in sl |

| subClass_i | in sl |

| enable_i | in sl |

| replEnable_i | in sl |

| scrEnable_i | in sl |

| inv_i | in sl |

| lmfc_i | in sl |

| nSync_i | in sl |

| gtTxReady_i | in sl |

| sysRef_i | in sl |

| status_o | out slv ( TX_STAT_WIDTH_C - 1 downto 0 ) |

| sampleData_i | in slv ( ( GT_WORD_SIZE_C * 8 ) - 1 downto 0 ) |

| r_jesdGtTx | out jesdGtTxLaneType |

Detailed Description

- See also

- entity

Definition at line 49 of file JesdTxLane.vhd.

Member Data Documentation

◆ TPD_G

|

Generic |

Definition at line 51 of file JesdTxLane.vhd.

◆ F_G

|

Generic |

Definition at line 52 of file JesdTxLane.vhd.

◆ K_G

|

Generic |

Definition at line 54 of file JesdTxLane.vhd.

◆ devClk_i

Definition at line 59 of file JesdTxLane.vhd.

◆ devRst_i

Definition at line 60 of file JesdTxLane.vhd.

◆ subClass_i

|

Port |

Definition at line 63 of file JesdTxLane.vhd.

◆ enable_i

Definition at line 66 of file JesdTxLane.vhd.

◆ replEnable_i

|

Port |

Definition at line 67 of file JesdTxLane.vhd.

◆ scrEnable_i

|

Port |

Definition at line 68 of file JesdTxLane.vhd.

◆ inv_i

Definition at line 69 of file JesdTxLane.vhd.

◆ lmfc_i

Definition at line 72 of file JesdTxLane.vhd.

◆ nSync_i

Definition at line 75 of file JesdTxLane.vhd.

◆ gtTxReady_i

|

Port |

Definition at line 78 of file JesdTxLane.vhd.

◆ sysRef_i

Definition at line 81 of file JesdTxLane.vhd.

◆ status_o

|

Port |

Definition at line 84 of file JesdTxLane.vhd.

◆ sampleData_i

|

Port |

Definition at line 87 of file JesdTxLane.vhd.

◆ r_jesdGtTx

|

Port |

Definition at line 91 of file JesdTxLane.vhd.

◆ ieee

|

Library |

Definition at line 39 of file JesdTxLane.vhd.

◆ std_logic_1164

|

Package |

Definition at line 40 of file JesdTxLane.vhd.

◆ std_logic_arith

|

Package |

Definition at line 41 of file JesdTxLane.vhd.

◆ std_logic_unsigned

|

Package |

Definition at line 42 of file JesdTxLane.vhd.

◆ StdRtlPkg

|

Package |

Definition at line 44 of file JesdTxLane.vhd.

◆ Jesd204bPkg

|

Package |

Definition at line 45 of file JesdTxLane.vhd.

The documentation for this class was generated from the following file:

- protocols/jesd204b/rtl/JesdTxLane.vhd