Inheritance diagram for Jesd204bRxGtx7:

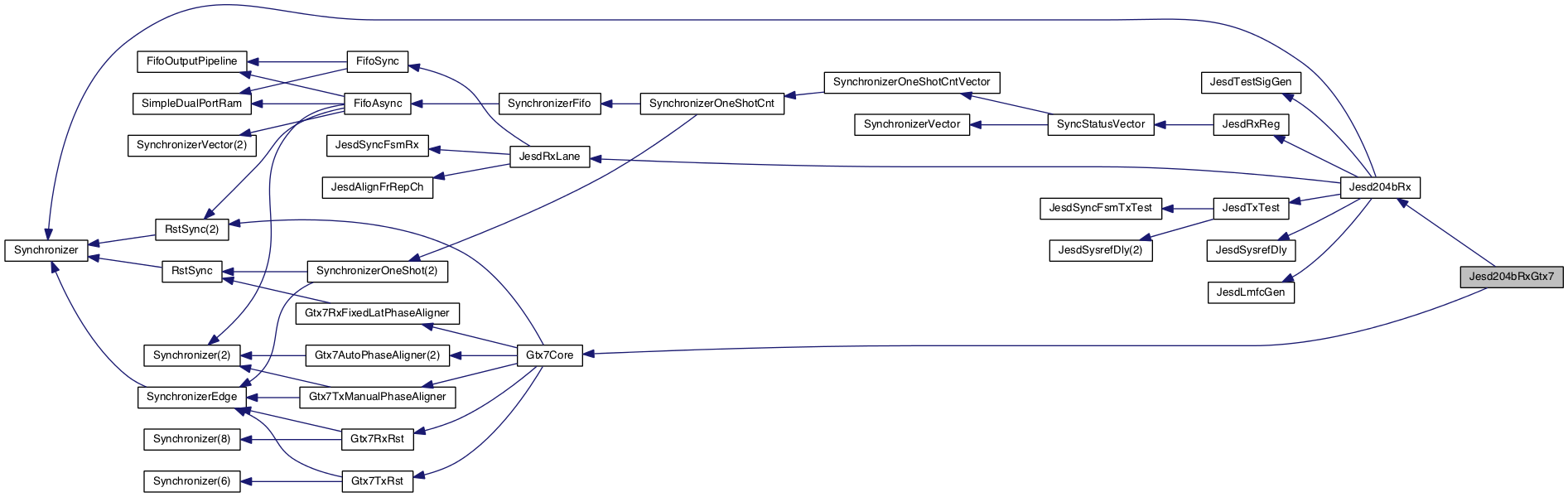

Inheritance diagram for Jesd204bRxGtx7: Collaboration diagram for Jesd204bRxGtx7:

Collaboration diagram for Jesd204bRxGtx7:Entities | |

| rtl | architecture |

Libraries | |

| ieee | |

| unisim | |

Use Clauses | |

| vcomponents | |

| std_logic_1164 | |

| std_logic_arith | |

| std_logic_unsigned | |

| numeric_std | |

| StdRtlPkg | Package <StdRtlPkg> |

| AxiLitePkg | Package <AxiLitePkg> |

| AxiStreamPkg | Package <AxiStreamPkg> |

| SsiPkg | Package <SsiPkg> |

| Jesd204bPkg | Package <Jesd204bPkg> |

Generics | |

| TPD_G | time := 1 ns |

| TEST_G | boolean := false |

| SYSREF_GEN_G | boolean := false |

| SIM_GTRESET_SPEEDUP_G | string := " FALSE " |

| SIM_VERSION_G | string := " 4.0 " |

| STABLE_CLOCK_PERIOD_G | real := 4 . 0E - 9 |

| CPLL_REFCLK_SEL_G | bit_vector := " 001 " |

| CPLL_FBDIV_G | integer |

| CPLL_FBDIV_45_G | integer |

| CPLL_REFCLK_DIV_G | integer |

| RXOUT_DIV_G | integer |

| RX_CLK25_DIV_G | integer |

| PMA_RSV_G | bit_vector := x " 001E7080 " |

| RX_OS_CFG_G | bit_vector := " 0000010000000 " |

| RXCDR_CFG_G | bit_vector := x " 03000023ff10400020 " |

| RXDFEXYDEN_G | sl := ' 1 ' |

| RX_DFE_KL_CFG2_G | bit_vector := X " 301148AC " |

| TX_PLL_G | string |

| RX_PLL_G | string |

| TXOUT_DIV_G | integer := 2 |

| TX_CLK25_DIV_G | integer := 7 |

| TX_BUF_EN_G | boolean := true |

| TX_OUTCLK_SRC_G | string := " OUTCLKPMA " |

| TX_DLY_BYPASS_G | sl := ' 1 ' |

| TX_PHASE_ALIGN_G | string := " NONE " |

| TX_BUF_ADDR_MODE_G | string := " FULL " |

| AXI_ERROR_RESP_G | slv ( 1 downto 0 ) := AXI_RESP_SLVERR_C |

| F_G | positive := 2 |

| K_G | positive := 32 |

| L_G | positive := 2 |

Ports | |

| rxOutClkOut | out slv ( L_G - 1 downto 0 ) |

| txOutClkOut | out slv ( L_G - 1 downto 0 ) |

| stableClk | in sl |

| qPllRefClkIn | in sl |

| qPllClkIn | in sl |

| qPllLockIn | in sl |

| qPllRefClkLostIn | in sl |

| qPllResetOut | out slv ( L_G - 1 downto 0 ) |

| cPllRefClkIn | in sl |

| cPllLockOut | out slv ( L_G - 1 downto 0 ) |

| gtTxP | out slv ( L_G - 1 downto 0 ) |

| gtTxN | out slv ( L_G - 1 downto 0 ) |

| gtRxP | in slv ( L_G - 1 downto 0 ) |

| gtRxN | in slv ( L_G - 1 downto 0 ) |

| devClk_i | in sl |

| devClk2_i | in sl |

| devRst_i | in sl |

| axiClk | in sl |

| axiRst | in sl |

| axilReadMaster | in AxiLiteReadMasterType |

| axilReadSlave | out AxiLiteReadSlaveType |

| axilWriteMaster | in AxiLiteWriteMasterType |

| axilWriteSlave | out AxiLiteWriteSlaveType |

| rxAxisMasterArr | out AxiStreamMasterArray ( L_G - 1 downto 0 ) |

| rxCtrlArr | in AxiStreamCtrlArray ( L_G - 1 downto 0 ) |

| sysRef_i | in sl |

| sysRef_o | out sl |

| nSync_o | out sl |

| leds_o | out slv ( 1 downto 0 ) |

| pulse_o | out slv ( L_G - 1 downto 0 ) |

| rxUserRdyOut | out slv ( 1 downto 0 ) |

| rxMmcmResetOut | out slv ( 1 downto 0 ) |

Detailed Description

Definition at line 35 of file Jesd204bRxGtx7.vhd.

Member Data Documentation

◆ TPD_G

|

Generic |

Definition at line 37 of file Jesd204bRxGtx7.vhd.

◆ TEST_G

|

Generic |

Definition at line 40 of file Jesd204bRxGtx7.vhd.

◆ SYSREF_GEN_G

|

Generic |

Definition at line 44 of file Jesd204bRxGtx7.vhd.

◆ SIM_GTRESET_SPEEDUP_G

|

Generic |

Definition at line 49 of file Jesd204bRxGtx7.vhd.

◆ SIM_VERSION_G

|

Generic |

Definition at line 50 of file Jesd204bRxGtx7.vhd.

◆ STABLE_CLOCK_PERIOD_G

|

Generic |

Definition at line 51 of file Jesd204bRxGtx7.vhd.

◆ CPLL_REFCLK_SEL_G

|

Generic |

Definition at line 54 of file Jesd204bRxGtx7.vhd.

◆ CPLL_FBDIV_G

|

Generic |

Definition at line 55 of file Jesd204bRxGtx7.vhd.

◆ CPLL_FBDIV_45_G

|

Generic |

Definition at line 56 of file Jesd204bRxGtx7.vhd.

◆ CPLL_REFCLK_DIV_G

|

Generic |

Definition at line 57 of file Jesd204bRxGtx7.vhd.

◆ RXOUT_DIV_G

|

Generic |

Definition at line 59 of file Jesd204bRxGtx7.vhd.

◆ RX_CLK25_DIV_G

|

Generic |

Definition at line 60 of file Jesd204bRxGtx7.vhd.

◆ PMA_RSV_G

|

Generic |

Definition at line 63 of file Jesd204bRxGtx7.vhd.

◆ RX_OS_CFG_G

|

Generic |

Definition at line 64 of file Jesd204bRxGtx7.vhd.

◆ RXCDR_CFG_G

|

Generic |

Definition at line 65 of file Jesd204bRxGtx7.vhd.

◆ RXDFEXYDEN_G

|

Generic |

Definition at line 66 of file Jesd204bRxGtx7.vhd.

◆ RX_DFE_KL_CFG2_G

|

Generic |

Definition at line 67 of file Jesd204bRxGtx7.vhd.

◆ TX_PLL_G

|

Generic |

Definition at line 70 of file Jesd204bRxGtx7.vhd.

◆ RX_PLL_G

|

Generic |

Definition at line 71 of file Jesd204bRxGtx7.vhd.

◆ TXOUT_DIV_G

|

Generic |

Definition at line 74 of file Jesd204bRxGtx7.vhd.

◆ TX_CLK25_DIV_G

|

Generic |

Definition at line 75 of file Jesd204bRxGtx7.vhd.

◆ TX_BUF_EN_G

|

Generic |

Definition at line 76 of file Jesd204bRxGtx7.vhd.

◆ TX_OUTCLK_SRC_G

|

Generic |

Definition at line 77 of file Jesd204bRxGtx7.vhd.

◆ TX_DLY_BYPASS_G

|

Generic |

Definition at line 78 of file Jesd204bRxGtx7.vhd.

◆ TX_PHASE_ALIGN_G

|

Generic |

Definition at line 79 of file Jesd204bRxGtx7.vhd.

◆ TX_BUF_ADDR_MODE_G

|

Generic |

Definition at line 80 of file Jesd204bRxGtx7.vhd.

◆ AXI_ERROR_RESP_G

|

Generic |

Definition at line 84 of file Jesd204bRxGtx7.vhd.

◆ F_G

|

Generic |

Definition at line 88 of file Jesd204bRxGtx7.vhd.

◆ K_G

|

Generic |

Definition at line 89 of file Jesd204bRxGtx7.vhd.

◆ L_G

|

Generic |

Definition at line 91 of file Jesd204bRxGtx7.vhd.

◆ rxOutClkOut

|

Port |

Definition at line 97 of file Jesd204bRxGtx7.vhd.

◆ txOutClkOut

|

Port |

Definition at line 98 of file Jesd204bRxGtx7.vhd.

◆ stableClk

Definition at line 101 of file Jesd204bRxGtx7.vhd.

◆ qPllRefClkIn

|

Port |

Definition at line 104 of file Jesd204bRxGtx7.vhd.

◆ qPllClkIn

Definition at line 105 of file Jesd204bRxGtx7.vhd.

◆ qPllLockIn

|

Port |

Definition at line 106 of file Jesd204bRxGtx7.vhd.

◆ qPllRefClkLostIn

|

Port |

Definition at line 107 of file Jesd204bRxGtx7.vhd.

◆ qPllResetOut

|

Port |

Definition at line 108 of file Jesd204bRxGtx7.vhd.

◆ cPllRefClkIn

|

Port |

Definition at line 111 of file Jesd204bRxGtx7.vhd.

◆ cPllLockOut

|

Port |

Definition at line 112 of file Jesd204bRxGtx7.vhd.

◆ gtTxP

Definition at line 115 of file Jesd204bRxGtx7.vhd.

◆ gtTxN

Definition at line 116 of file Jesd204bRxGtx7.vhd.

◆ gtRxP

Definition at line 117 of file Jesd204bRxGtx7.vhd.

◆ gtRxN

Definition at line 118 of file Jesd204bRxGtx7.vhd.

◆ devClk_i

Definition at line 122 of file Jesd204bRxGtx7.vhd.

◆ devClk2_i

Definition at line 123 of file Jesd204bRxGtx7.vhd.

◆ devRst_i

Definition at line 124 of file Jesd204bRxGtx7.vhd.

◆ axiClk

Definition at line 128 of file Jesd204bRxGtx7.vhd.

◆ axiRst

Definition at line 129 of file Jesd204bRxGtx7.vhd.

◆ axilReadMaster

|

Port |

Definition at line 132 of file Jesd204bRxGtx7.vhd.

◆ axilReadSlave

|

Port |

Definition at line 133 of file Jesd204bRxGtx7.vhd.

◆ axilWriteMaster

Definition at line 134 of file Jesd204bRxGtx7.vhd.

◆ axilWriteSlave

|

Port |

Definition at line 135 of file Jesd204bRxGtx7.vhd.

◆ rxAxisMasterArr

|

Port |

Definition at line 138 of file Jesd204bRxGtx7.vhd.

◆ rxCtrlArr

|

Port |

Definition at line 139 of file Jesd204bRxGtx7.vhd.

◆ sysRef_i

Definition at line 145 of file Jesd204bRxGtx7.vhd.

◆ sysRef_o

Definition at line 148 of file Jesd204bRxGtx7.vhd.

◆ nSync_o

Definition at line 151 of file Jesd204bRxGtx7.vhd.

◆ leds_o

Definition at line 154 of file Jesd204bRxGtx7.vhd.

◆ pulse_o

Definition at line 157 of file Jesd204bRxGtx7.vhd.

◆ rxUserRdyOut

|

Port |

Definition at line 160 of file Jesd204bRxGtx7.vhd.

◆ rxMmcmResetOut

|

Port |

Definition at line 163 of file Jesd204bRxGtx7.vhd.

◆ ieee

|

Library |

Definition at line 20 of file Jesd204bRxGtx7.vhd.

◆ unisim

|

Library |

Definition at line 21 of file Jesd204bRxGtx7.vhd.

◆ vcomponents

|

Package |

Definition at line 22 of file Jesd204bRxGtx7.vhd.

◆ std_logic_1164

|

Package |

Definition at line 24 of file Jesd204bRxGtx7.vhd.

◆ std_logic_arith

|

Package |

Definition at line 25 of file Jesd204bRxGtx7.vhd.

◆ std_logic_unsigned

|

Package |

Definition at line 26 of file Jesd204bRxGtx7.vhd.

◆ numeric_std

|

Package |

Definition at line 27 of file Jesd204bRxGtx7.vhd.

◆ StdRtlPkg

|

Package |

Definition at line 29 of file Jesd204bRxGtx7.vhd.

◆ AxiLitePkg

|

Package |

Definition at line 30 of file Jesd204bRxGtx7.vhd.

◆ AxiStreamPkg

|

Package |

Definition at line 31 of file Jesd204bRxGtx7.vhd.

◆ SsiPkg

|

Package |

Definition at line 32 of file Jesd204bRxGtx7.vhd.

◆ Jesd204bPkg

|

Package |

Definition at line 33 of file Jesd204bRxGtx7.vhd.

The documentation for this class was generated from the following file:

- protocols/jesd204b/example/Jesd204bRxGtx7.vhd