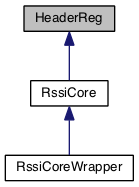

Inheritance diagram for HeaderReg:

Inheritance diagram for HeaderReg:Entities | |

| rtl | architecture |

Libraries | |

| ieee | |

Use Clauses | |

| std_logic_1164 | |

| std_logic_unsigned | |

| std_logic_arith | |

| StdRtlPkg | Package <StdRtlPkg> |

| RssiPkg | Package <RssiPkg> |

| math_real | |

Generics | |

| TPD_G | time := 1 ns |

| SYN_HEADER_SIZE_G | natural := 24 |

| ACK_HEADER_SIZE_G | natural := 8 |

| EACK_HEADER_SIZE_G | natural := 8 |

| RST_HEADER_SIZE_G | natural := 8 |

| NULL_HEADER_SIZE_G | natural := 8 |

| DATA_HEADER_SIZE_G | natural := 8 |

Ports | |

| clk_i | in sl |

| rst_i | in sl |

| synHeadSt_i | in sl |

| rstHeadSt_i | in sl |

| dataHeadSt_i | in sl |

| nullHeadSt_i | in sl |

| ackHeadSt_i | in sl |

| ack_i | in sl |

| txSeqN_i | in slv ( 7 downto 0 ) |

| rxAckN_i | in slv ( 7 downto 0 ) |

| headerValues_i | in RssiParamType |

| addr_i | in slv ( 7 downto 0 ) |

| headerData_o | out slv ( ( RSSI_WORD_WIDTH_C * 8 ) - 1 downto 0 ) |

| ready_o | out sl |

| headerLength_o | out positive |

Detailed Description

- See also

- entity

Definition at line 32 of file HeaderReg.vhd.

Member Data Documentation

◆ TPD_G

|

Generic |

Definition at line 34 of file HeaderReg.vhd.

◆ SYN_HEADER_SIZE_G

|

Generic |

Definition at line 36 of file HeaderReg.vhd.

◆ ACK_HEADER_SIZE_G

|

Generic |

Definition at line 37 of file HeaderReg.vhd.

◆ EACK_HEADER_SIZE_G

|

Generic |

Definition at line 38 of file HeaderReg.vhd.

◆ RST_HEADER_SIZE_G

|

Generic |

Definition at line 39 of file HeaderReg.vhd.

◆ NULL_HEADER_SIZE_G

|

Generic |

Definition at line 40 of file HeaderReg.vhd.

◆ DATA_HEADER_SIZE_G

|

Generic |

Definition at line 42 of file HeaderReg.vhd.

◆ clk_i

Definition at line 44 of file HeaderReg.vhd.

◆ rst_i

Definition at line 45 of file HeaderReg.vhd.

◆ synHeadSt_i

|

Port |

Definition at line 48 of file HeaderReg.vhd.

◆ rstHeadSt_i

|

Port |

Definition at line 49 of file HeaderReg.vhd.

◆ dataHeadSt_i

|

Port |

Definition at line 50 of file HeaderReg.vhd.

◆ nullHeadSt_i

|

Port |

Definition at line 51 of file HeaderReg.vhd.

◆ ackHeadSt_i

|

Port |

Definition at line 52 of file HeaderReg.vhd.

◆ ack_i

Definition at line 56 of file HeaderReg.vhd.

◆ txSeqN_i

Definition at line 59 of file HeaderReg.vhd.

◆ rxAckN_i

Definition at line 60 of file HeaderReg.vhd.

◆ headerValues_i

|

Port |

Definition at line 63 of file HeaderReg.vhd.

◆ addr_i

Definition at line 69 of file HeaderReg.vhd.

◆ headerData_o

|

Port |

Definition at line 70 of file HeaderReg.vhd.

◆ ready_o

Definition at line 71 of file HeaderReg.vhd.

◆ headerLength_o

|

Port |

Definition at line 73 of file HeaderReg.vhd.

◆ ieee

|

Library |

Definition at line 21 of file HeaderReg.vhd.

◆ std_logic_1164

|

Package |

Definition at line 22 of file HeaderReg.vhd.

◆ std_logic_unsigned

|

Package |

Definition at line 23 of file HeaderReg.vhd.

◆ std_logic_arith

|

Package |

Definition at line 24 of file HeaderReg.vhd.

◆ StdRtlPkg

|

Package |

Definition at line 26 of file HeaderReg.vhd.

◆ RssiPkg

|

Package |

Definition at line 27 of file HeaderReg.vhd.

◆ math_real

|

Package |

Definition at line 28 of file HeaderReg.vhd.

The documentation for this class was generated from the following file:

- protocols/rssi/rtl/HeaderReg.vhd