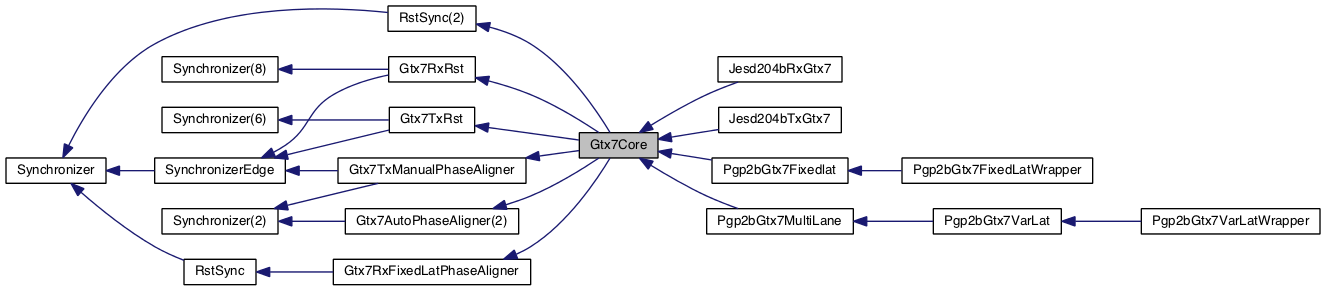

Inheritance diagram for Gtx7Core:

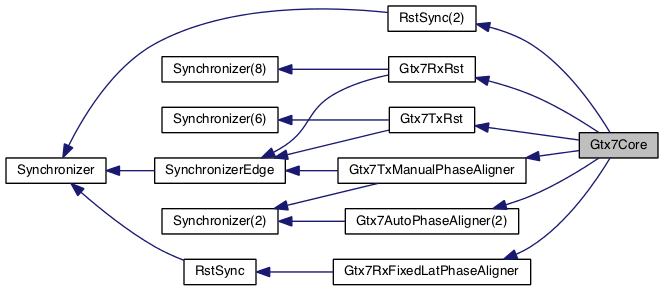

Inheritance diagram for Gtx7Core: Collaboration diagram for Gtx7Core:

Collaboration diagram for Gtx7Core:Entities | |

| rtl | architecture |

Libraries | |

| ieee | |

| UNISIM | |

Use Clauses | |

| std_logic_1164 | |

| math_real | |

| StdRtlPkg | Package <StdRtlPkg> |

| VCOMPONENTS | |

Generics | |

| TPD_G | time := 1 ns |

| SIM_GTRESET_SPEEDUP_G | string := " FALSE " |

| SIM_VERSION_G | string := " 4.0 " |

| SIMULATION_G | boolean := false |

| STABLE_CLOCK_PERIOD_G | real := 4 . 0E - 9 |

| CPLL_REFCLK_SEL_G | bit_vector := " 001 " |

| CPLL_FBDIV_G | integer := 4 |

| CPLL_FBDIV_45_G | integer := 5 |

| CPLL_REFCLK_DIV_G | integer := 1 |

| RXOUT_DIV_G | integer := 2 |

| TXOUT_DIV_G | integer := 2 |

| RX_CLK25_DIV_G | integer := 5 |

| TX_CLK25_DIV_G | integer := 5 |

| PMA_RSV_G | bit_vector := X " 00018480 " |

| RX_OS_CFG_G | bit_vector := " 0000010000000 " |

| RXCDR_CFG_G | bit_vector := x " 03000023ff40200020 " |

| TX_PLL_G | string := " CPLL " |

| RX_PLL_G | string := " CPLL " |

| TX_EXT_DATA_WIDTH_G | integer := 16 |

| TX_INT_DATA_WIDTH_G | integer := 20 |

| TX_8B10B_EN_G | boolean := true |

| RX_EXT_DATA_WIDTH_G | integer := 16 |

| RX_INT_DATA_WIDTH_G | integer := 20 |

| RX_8B10B_EN_G | boolean := true |

| TX_BUF_EN_G | boolean := true |

| TX_OUTCLK_SRC_G | string := " PLLREFCLK " |

| TX_DLY_BYPASS_G | sl := ' 1 ' |

| TX_PHASE_ALIGN_G | string := " AUTO " |

| TX_BUF_ADDR_MODE_G | string := " FAST " |

| RX_BUF_EN_G | boolean := true |

| RX_OUTCLK_SRC_G | string := " PLLREFCLK " |

| RX_USRCLK_SRC_G | string := " RXOUTCLK " |

| RX_DLY_BYPASS_G | sl := ' 1 ' |

| RX_DDIEN_G | sl := ' 0 ' |

| RX_BUF_ADDR_MODE_G | string := " FAST " |

| RX_ALIGN_MODE_G | string := " GT " |

| ALIGN_COMMA_DOUBLE_G | string := " FALSE " |

| ALIGN_COMMA_ENABLE_G | bit_vector := " 1111111111 " |

| ALIGN_COMMA_WORD_G | integer := 2 |

| ALIGN_MCOMMA_DET_G | string := " FALSE " |

| ALIGN_MCOMMA_VALUE_G | bit_vector := " 1010000011 " |

| ALIGN_MCOMMA_EN_G | sl := ' 0 ' |

| ALIGN_PCOMMA_DET_G | string := " FALSE " |

| ALIGN_PCOMMA_VALUE_G | bit_vector := " 0101111100 " |

| ALIGN_PCOMMA_EN_G | sl := ' 0 ' |

| SHOW_REALIGN_COMMA_G | string := " FALSE " |

| RXSLIDE_MODE_G | string := " PCS " |

| FIXED_COMMA_EN_G | slv ( 3 downto 0 ) := " 0011 " |

| FIXED_ALIGN_COMMA_0_G | slv := " ----------0101111100 " |

| FIXED_ALIGN_COMMA_1_G | slv := " ----------1010000011 " |

| FIXED_ALIGN_COMMA_2_G | slv := " XXXXXXXXXXXXXXXXXXXX " |

| FIXED_ALIGN_COMMA_3_G | slv := " XXXXXXXXXXXXXXXXXXXX " |

| RX_DISPERR_SEQ_MATCH_G | string := " TRUE " |

| DEC_MCOMMA_DETECT_G | string := " TRUE " |

| DEC_PCOMMA_DETECT_G | string := " TRUE " |

| DEC_VALID_COMMA_ONLY_G | string := " FALSE " |

| CBCC_DATA_SOURCE_SEL_G | string := " DECODED " |

| CLK_COR_SEQ_2_USE_G | string := " FALSE " |

| CLK_COR_KEEP_IDLE_G | string := " FALSE " |

| CLK_COR_MAX_LAT_G | integer := 9 |

| CLK_COR_MIN_LAT_G | integer := 7 |

| CLK_COR_PRECEDENCE_G | string := " TRUE " |

| CLK_COR_REPEAT_WAIT_G | integer := 0 |

| CLK_COR_SEQ_LEN_G | integer := 1 |

| CLK_COR_SEQ_1_ENABLE_G | bit_vector := " 1111 " |

| CLK_COR_SEQ_1_1_G | bit_vector := " 0100000000 " |

| CLK_COR_SEQ_1_2_G | bit_vector := " 0000000000 " |

| CLK_COR_SEQ_1_3_G | bit_vector := " 0000000000 " |

| CLK_COR_SEQ_1_4_G | bit_vector := " 0000000000 " |

| CLK_CORRECT_USE_G | string := " FALSE " |

| CLK_COR_SEQ_2_ENABLE_G | bit_vector := " 0000 " |

| CLK_COR_SEQ_2_1_G | bit_vector := " 0100000000 " |

| CLK_COR_SEQ_2_2_G | bit_vector := " 0000000000 " |

| CLK_COR_SEQ_2_3_G | bit_vector := " 0000000000 " |

| CLK_COR_SEQ_2_4_G | bit_vector := " 0000000000 " |

| RX_CHAN_BOND_EN_G | boolean := false |

| RX_CHAN_BOND_MASTER_G | boolean := false |

| CHAN_BOND_KEEP_ALIGN_G | string := " FALSE " |

| CHAN_BOND_MAX_SKEW_G | integer := 1 |

| CHAN_BOND_SEQ_LEN_G | integer := 1 |

| CHAN_BOND_SEQ_1_1_G | bit_vector := " 0000000000 " |

| CHAN_BOND_SEQ_1_2_G | bit_vector := " 0000000000 " |

| CHAN_BOND_SEQ_1_3_G | bit_vector := " 0000000000 " |

| CHAN_BOND_SEQ_1_4_G | bit_vector := " 0000000000 " |

| CHAN_BOND_SEQ_1_ENABLE_G | bit_vector := " 1111 " |

| CHAN_BOND_SEQ_2_1_G | bit_vector := " 0000000000 " |

| CHAN_BOND_SEQ_2_2_G | bit_vector := " 0000000000 " |

| CHAN_BOND_SEQ_2_3_G | bit_vector := " 0000000000 " |

| CHAN_BOND_SEQ_2_4_G | bit_vector := " 0000000000 " |

| CHAN_BOND_SEQ_2_ENABLE_G | bit_vector := " 0000 " |

| CHAN_BOND_SEQ_2_USE_G | string := " FALSE " |

| FTS_DESKEW_SEQ_ENABLE_G | bit_vector := " 1111 " |

| FTS_LANE_DESKEW_CFG_G | bit_vector := " 1111 " |

| FTS_LANE_DESKEW_EN_G | string := " FALSE " |

| RX_EQUALIZER_G | string := " DFE " |

| RX_DFE_KL_CFG2_G | bit_vector := x " 3008E56A " |

| RX_CM_TRIM_G | bit_vector := " 010 " |

| RX_DFE_LPM_CFG_G | bit_vector := x " 0954 " |

| RXDFELFOVRDEN_G | sl := ' 1 ' |

| RXDFEXYDEN_G | sl := ' 1 ' |

Ports | |

| stableClkIn | in sl |

| cPllRefClkIn | in sl := ' 0 ' |

| cPllLockOut | out sl |

| qPllRefClkIn | in sl := ' 0 ' |

| qPllClkIn | in sl := ' 0 ' |

| qPllLockIn | in sl := ' 0 ' |

| qPllRefClkLostIn | in sl := ' 0 ' |

| qPllResetOut | out sl |

| gtRxRefClkBufg | in sl := ' 0 ' |

| gtTxP | out sl |

| gtTxN | out sl |

| gtRxP | in sl |

| gtRxN | in sl |

| rxOutClkOut | out sl |

| rxUsrClkIn | in sl |

| rxUsrClk2In | in sl |

| rxUserRdyOut | out sl |

| rxMmcmResetOut | out sl |

| rxMmcmLockedIn | in sl := ' 1 ' |

| rxUserResetIn | in sl |

| rxResetDoneOut | out sl |

| rxDataValidIn | in sl := ' 1 ' |

| rxSlideIn | in sl := ' 0 ' |

| rxDataOut | out slv ( RX_EXT_DATA_WIDTH_G - 1 downto 0 ) |

| rxCharIsKOut | out slv ( ( RX_EXT_DATA_WIDTH_G / 8 ) - 1 downto 0 ) |

| rxDecErrOut | out slv ( ( RX_EXT_DATA_WIDTH_G / 8 ) - 1 downto 0 ) |

| rxDispErrOut | out slv ( ( RX_EXT_DATA_WIDTH_G / 8 ) - 1 downto 0 ) |

| rxPolarityIn | in sl := ' 0 ' |

| rxBufStatusOut | out slv ( 2 downto 0 ) |

| rxChBondLevelIn | in slv ( 2 downto 0 ) := " 000 " |

| rxChBondIn | in slv ( 4 downto 0 ) := " 00000 " |

| rxChBondOut | out slv ( 4 downto 0 ) |

| txOutClkOut | out sl |

| txUsrClkIn | in sl |

| txUsrClk2In | in sl |

| txUserRdyOut | out sl |

| txMmcmResetOut | out sl |

| txMmcmLockedIn | in sl := ' 1 ' |

| txUserResetIn | in sl |

| txResetDoneOut | out sl |

| txDataIn | in slv ( TX_EXT_DATA_WIDTH_G - 1 downto 0 ) |

| txCharIsKIn | in slv ( ( TX_EXT_DATA_WIDTH_G / 8 ) - 1 downto 0 ) |

| txBufStatusOut | out slv ( 1 downto 0 ) |

| txPolarityIn | in sl := ' 0 ' |

| txPowerDown | in slv ( 1 downto 0 ) := " 00 " |

| rxPowerDown | in slv ( 1 downto 0 ) := " 00 " |

| loopbackIn | in slv ( 2 downto 0 ) := " 000 " |

| txPreCursor | in slv ( 4 downto 0 ) := ( others = > ' 0 ' ) |

| txPostCursor | in slv ( 4 downto 0 ) := ( others = > ' 0 ' ) |

| txDiffCtrl | in slv ( 3 downto 0 ) := " 1000 " |

| drpClk | in sl := ' 0 ' |

| drpRdy | out sl |

| drpEn | in sl := ' 0 ' |

| drpWe | in sl := ' 0 ' |

| drpAddr | in slv ( 8 downto 0 ) := " 000000000 " |

| drpDi | in slv ( 15 downto 0 ) := X " 0000 " |

| drpDo | out slv ( 15 downto 0 ) |

Detailed Description

- See also

- entity

Definition at line 29 of file Gtx7Core.vhd.

Member Data Documentation

◆ TPD_G

|

Generic |

Definition at line 32 of file Gtx7Core.vhd.

◆ SIM_GTRESET_SPEEDUP_G

|

Generic |

Definition at line 35 of file Gtx7Core.vhd.

◆ SIM_VERSION_G

|

Generic |

Definition at line 36 of file Gtx7Core.vhd.

◆ SIMULATION_G

|

Generic |

Definition at line 38 of file Gtx7Core.vhd.

◆ STABLE_CLOCK_PERIOD_G

|

Generic |

Definition at line 40 of file Gtx7Core.vhd.

◆ CPLL_REFCLK_SEL_G

|

Generic |

Definition at line 43 of file Gtx7Core.vhd.

◆ CPLL_FBDIV_G

|

Generic |

Definition at line 44 of file Gtx7Core.vhd.

◆ CPLL_FBDIV_45_G

|

Generic |

Definition at line 45 of file Gtx7Core.vhd.

◆ CPLL_REFCLK_DIV_G

|

Generic |

Definition at line 46 of file Gtx7Core.vhd.

◆ RXOUT_DIV_G

|

Generic |

Definition at line 47 of file Gtx7Core.vhd.

◆ TXOUT_DIV_G

|

Generic |

Definition at line 48 of file Gtx7Core.vhd.

◆ RX_CLK25_DIV_G

|

Generic |

Definition at line 49 of file Gtx7Core.vhd.

◆ TX_CLK25_DIV_G

|

Generic |

Definition at line 50 of file Gtx7Core.vhd.

◆ PMA_RSV_G

|

Generic |

Definition at line 53 of file Gtx7Core.vhd.

◆ RX_OS_CFG_G

|

Generic |

Definition at line 55 of file Gtx7Core.vhd.

◆ RXCDR_CFG_G

|

Generic |

Definition at line 56 of file Gtx7Core.vhd.

◆ TX_PLL_G

|

Generic |

Definition at line 60 of file Gtx7Core.vhd.

◆ RX_PLL_G

|

Generic |

Definition at line 61 of file Gtx7Core.vhd.

◆ TX_EXT_DATA_WIDTH_G

|

Generic |

Definition at line 64 of file Gtx7Core.vhd.

◆ TX_INT_DATA_WIDTH_G

|

Generic |

Definition at line 65 of file Gtx7Core.vhd.

◆ TX_8B10B_EN_G

|

Generic |

Definition at line 66 of file Gtx7Core.vhd.

◆ RX_EXT_DATA_WIDTH_G

|

Generic |

Definition at line 68 of file Gtx7Core.vhd.

◆ RX_INT_DATA_WIDTH_G

|

Generic |

Definition at line 69 of file Gtx7Core.vhd.

◆ RX_8B10B_EN_G

|

Generic |

Definition at line 70 of file Gtx7Core.vhd.

◆ TX_BUF_EN_G

|

Generic |

Definition at line 73 of file Gtx7Core.vhd.

◆ TX_OUTCLK_SRC_G

|

Generic |

Definition at line 74 of file Gtx7Core.vhd.

◆ TX_DLY_BYPASS_G

|

Generic |

Definition at line 75 of file Gtx7Core.vhd.

◆ TX_PHASE_ALIGN_G

|

Generic |

Definition at line 76 of file Gtx7Core.vhd.

◆ TX_BUF_ADDR_MODE_G

|

Generic |

Definition at line 77 of file Gtx7Core.vhd.

◆ RX_BUF_EN_G

|

Generic |

Definition at line 79 of file Gtx7Core.vhd.

◆ RX_OUTCLK_SRC_G

|

Generic |

Definition at line 80 of file Gtx7Core.vhd.

◆ RX_USRCLK_SRC_G

|

Generic |

Definition at line 81 of file Gtx7Core.vhd.

◆ RX_DLY_BYPASS_G

|

Generic |

Definition at line 82 of file Gtx7Core.vhd.

◆ RX_DDIEN_G

|

Generic |

Definition at line 83 of file Gtx7Core.vhd.

◆ RX_BUF_ADDR_MODE_G

|

Generic |

Definition at line 84 of file Gtx7Core.vhd.

◆ RX_ALIGN_MODE_G

|

Generic |

Definition at line 87 of file Gtx7Core.vhd.

◆ ALIGN_COMMA_DOUBLE_G

|

Generic |

Definition at line 88 of file Gtx7Core.vhd.

◆ ALIGN_COMMA_ENABLE_G

|

Generic |

Definition at line 89 of file Gtx7Core.vhd.

◆ ALIGN_COMMA_WORD_G

|

Generic |

Definition at line 90 of file Gtx7Core.vhd.

◆ ALIGN_MCOMMA_DET_G

|

Generic |

Definition at line 91 of file Gtx7Core.vhd.

◆ ALIGN_MCOMMA_VALUE_G

|

Generic |

Definition at line 92 of file Gtx7Core.vhd.

◆ ALIGN_MCOMMA_EN_G

|

Generic |

Definition at line 93 of file Gtx7Core.vhd.

◆ ALIGN_PCOMMA_DET_G

|

Generic |

Definition at line 94 of file Gtx7Core.vhd.

◆ ALIGN_PCOMMA_VALUE_G

|

Generic |

Definition at line 95 of file Gtx7Core.vhd.

◆ ALIGN_PCOMMA_EN_G

|

Generic |

Definition at line 96 of file Gtx7Core.vhd.

◆ SHOW_REALIGN_COMMA_G

|

Generic |

Definition at line 97 of file Gtx7Core.vhd.

◆ RXSLIDE_MODE_G

|

Generic |

Definition at line 98 of file Gtx7Core.vhd.

◆ FIXED_COMMA_EN_G

|

Generic |

Definition at line 101 of file Gtx7Core.vhd.

◆ FIXED_ALIGN_COMMA_0_G

|

Generic |

Definition at line 102 of file Gtx7Core.vhd.

◆ FIXED_ALIGN_COMMA_1_G

|

Generic |

Definition at line 103 of file Gtx7Core.vhd.

◆ FIXED_ALIGN_COMMA_2_G

|

Generic |

Definition at line 104 of file Gtx7Core.vhd.

◆ FIXED_ALIGN_COMMA_3_G

|

Generic |

Definition at line 105 of file Gtx7Core.vhd.

◆ RX_DISPERR_SEQ_MATCH_G

|

Generic |

Definition at line 108 of file Gtx7Core.vhd.

◆ DEC_MCOMMA_DETECT_G

|

Generic |

Definition at line 109 of file Gtx7Core.vhd.

◆ DEC_PCOMMA_DETECT_G

|

Generic |

Definition at line 110 of file Gtx7Core.vhd.

◆ DEC_VALID_COMMA_ONLY_G

|

Generic |

Definition at line 111 of file Gtx7Core.vhd.

◆ CBCC_DATA_SOURCE_SEL_G

|

Generic |

Definition at line 114 of file Gtx7Core.vhd.

◆ CLK_COR_SEQ_2_USE_G

|

Generic |

Definition at line 115 of file Gtx7Core.vhd.

◆ CLK_COR_KEEP_IDLE_G

|

Generic |

Definition at line 116 of file Gtx7Core.vhd.

◆ CLK_COR_MAX_LAT_G

|

Generic |

Definition at line 117 of file Gtx7Core.vhd.

◆ CLK_COR_MIN_LAT_G

|

Generic |

Definition at line 118 of file Gtx7Core.vhd.

◆ CLK_COR_PRECEDENCE_G

|

Generic |

Definition at line 119 of file Gtx7Core.vhd.

◆ CLK_COR_REPEAT_WAIT_G

|

Generic |

Definition at line 120 of file Gtx7Core.vhd.

◆ CLK_COR_SEQ_LEN_G

|

Generic |

Definition at line 121 of file Gtx7Core.vhd.

◆ CLK_COR_SEQ_1_ENABLE_G

|

Generic |

Definition at line 122 of file Gtx7Core.vhd.

◆ CLK_COR_SEQ_1_1_G

|

Generic |

Definition at line 123 of file Gtx7Core.vhd.

◆ CLK_COR_SEQ_1_2_G

|

Generic |

Definition at line 124 of file Gtx7Core.vhd.

◆ CLK_COR_SEQ_1_3_G

|

Generic |

Definition at line 125 of file Gtx7Core.vhd.

◆ CLK_COR_SEQ_1_4_G

|

Generic |

Definition at line 126 of file Gtx7Core.vhd.

◆ CLK_CORRECT_USE_G

|

Generic |

Definition at line 127 of file Gtx7Core.vhd.

◆ CLK_COR_SEQ_2_ENABLE_G

|

Generic |

Definition at line 128 of file Gtx7Core.vhd.

◆ CLK_COR_SEQ_2_1_G

|

Generic |

Definition at line 129 of file Gtx7Core.vhd.

◆ CLK_COR_SEQ_2_2_G

|

Generic |

Definition at line 130 of file Gtx7Core.vhd.

◆ CLK_COR_SEQ_2_3_G

|

Generic |

Definition at line 131 of file Gtx7Core.vhd.

◆ CLK_COR_SEQ_2_4_G

|

Generic |

Definition at line 132 of file Gtx7Core.vhd.

◆ RX_CHAN_BOND_EN_G

|

Generic |

Definition at line 135 of file Gtx7Core.vhd.

◆ RX_CHAN_BOND_MASTER_G

|

Generic |

Definition at line 136 of file Gtx7Core.vhd.

◆ CHAN_BOND_KEEP_ALIGN_G

|

Generic |

Definition at line 137 of file Gtx7Core.vhd.

◆ CHAN_BOND_MAX_SKEW_G

|

Generic |

Definition at line 138 of file Gtx7Core.vhd.

◆ CHAN_BOND_SEQ_LEN_G

|

Generic |

Definition at line 139 of file Gtx7Core.vhd.

◆ CHAN_BOND_SEQ_1_1_G

|

Generic |

Definition at line 140 of file Gtx7Core.vhd.

◆ CHAN_BOND_SEQ_1_2_G

|

Generic |

Definition at line 141 of file Gtx7Core.vhd.

◆ CHAN_BOND_SEQ_1_3_G

|

Generic |

Definition at line 142 of file Gtx7Core.vhd.

◆ CHAN_BOND_SEQ_1_4_G

|

Generic |

Definition at line 143 of file Gtx7Core.vhd.

◆ CHAN_BOND_SEQ_1_ENABLE_G

|

Generic |

Definition at line 144 of file Gtx7Core.vhd.

◆ CHAN_BOND_SEQ_2_1_G

|

Generic |

Definition at line 145 of file Gtx7Core.vhd.

◆ CHAN_BOND_SEQ_2_2_G

|

Generic |

Definition at line 146 of file Gtx7Core.vhd.

◆ CHAN_BOND_SEQ_2_3_G

|

Generic |

Definition at line 147 of file Gtx7Core.vhd.

◆ CHAN_BOND_SEQ_2_4_G

|

Generic |

Definition at line 148 of file Gtx7Core.vhd.

◆ CHAN_BOND_SEQ_2_ENABLE_G

|

Generic |

Definition at line 149 of file Gtx7Core.vhd.

◆ CHAN_BOND_SEQ_2_USE_G

|

Generic |

Definition at line 150 of file Gtx7Core.vhd.

◆ FTS_DESKEW_SEQ_ENABLE_G

|

Generic |

Definition at line 151 of file Gtx7Core.vhd.

◆ FTS_LANE_DESKEW_CFG_G

|

Generic |

Definition at line 152 of file Gtx7Core.vhd.

◆ FTS_LANE_DESKEW_EN_G

|

Generic |

Definition at line 153 of file Gtx7Core.vhd.

◆ RX_EQUALIZER_G

|

Generic |

Definition at line 156 of file Gtx7Core.vhd.

◆ RX_DFE_KL_CFG2_G

|

Generic |

Definition at line 157 of file Gtx7Core.vhd.

◆ RX_CM_TRIM_G

|

Generic |

Definition at line 158 of file Gtx7Core.vhd.

◆ RX_DFE_LPM_CFG_G

|

Generic |

Definition at line 159 of file Gtx7Core.vhd.

◆ RXDFELFOVRDEN_G

|

Generic |

Definition at line 160 of file Gtx7Core.vhd.

◆ RXDFEXYDEN_G

|

Generic |

Definition at line 162 of file Gtx7Core.vhd.

◆ stableClkIn

|

Port |

Definition at line 165 of file Gtx7Core.vhd.

◆ cPllRefClkIn

|

Port |

Definition at line 167 of file Gtx7Core.vhd.

◆ cPllLockOut

|

Port |

Definition at line 168 of file Gtx7Core.vhd.

◆ qPllRefClkIn

|

Port |

Definition at line 170 of file Gtx7Core.vhd.

◆ qPllClkIn

Definition at line 171 of file Gtx7Core.vhd.

◆ qPllLockIn

|

Port |

Definition at line 172 of file Gtx7Core.vhd.

◆ qPllRefClkLostIn

|

Port |

Definition at line 173 of file Gtx7Core.vhd.

◆ qPllResetOut

|

Port |

Definition at line 174 of file Gtx7Core.vhd.

◆ gtRxRefClkBufg

|

Port |

Definition at line 175 of file Gtx7Core.vhd.

◆ gtTxP

Definition at line 179 of file Gtx7Core.vhd.

◆ gtTxN

Definition at line 180 of file Gtx7Core.vhd.

◆ gtRxP

Definition at line 181 of file Gtx7Core.vhd.

◆ gtRxN

Definition at line 182 of file Gtx7Core.vhd.

◆ rxOutClkOut

|

Port |

Definition at line 185 of file Gtx7Core.vhd.

◆ rxUsrClkIn

|

Port |

Definition at line 186 of file Gtx7Core.vhd.

◆ rxUsrClk2In

|

Port |

Definition at line 187 of file Gtx7Core.vhd.

◆ rxUserRdyOut

|

Port |

Definition at line 188 of file Gtx7Core.vhd.

◆ rxMmcmResetOut

|

Port |

Definition at line 189 of file Gtx7Core.vhd.

◆ rxMmcmLockedIn

|

Port |

Definition at line 190 of file Gtx7Core.vhd.

◆ rxUserResetIn

|

Port |

Definition at line 193 of file Gtx7Core.vhd.

◆ rxResetDoneOut

|

Port |

Definition at line 194 of file Gtx7Core.vhd.

◆ rxDataValidIn

|

Port |

Definition at line 197 of file Gtx7Core.vhd.

◆ rxSlideIn

Definition at line 198 of file Gtx7Core.vhd.

◆ rxDataOut

|

Port |

Definition at line 201 of file Gtx7Core.vhd.

◆ rxCharIsKOut

|

Port |

Definition at line 202 of file Gtx7Core.vhd.

◆ rxDecErrOut

|

Port |

Definition at line 203 of file Gtx7Core.vhd.

◆ rxDispErrOut

|

Port |

Definition at line 204 of file Gtx7Core.vhd.

◆ rxPolarityIn

|

Port |

Definition at line 205 of file Gtx7Core.vhd.

◆ rxBufStatusOut

|

Port |

Definition at line 206 of file Gtx7Core.vhd.

◆ rxChBondLevelIn

|

Port |

Definition at line 209 of file Gtx7Core.vhd.

◆ rxChBondIn

|

Port |

Definition at line 210 of file Gtx7Core.vhd.

◆ rxChBondOut

|

Port |

Definition at line 211 of file Gtx7Core.vhd.

◆ txOutClkOut

|

Port |

Definition at line 214 of file Gtx7Core.vhd.

◆ txUsrClkIn

|

Port |

Definition at line 215 of file Gtx7Core.vhd.

◆ txUsrClk2In

|

Port |

Definition at line 216 of file Gtx7Core.vhd.

◆ txUserRdyOut

|

Port |

Definition at line 217 of file Gtx7Core.vhd.

◆ txMmcmResetOut

|

Port |

Definition at line 218 of file Gtx7Core.vhd.

◆ txMmcmLockedIn

|

Port |

Definition at line 219 of file Gtx7Core.vhd.

◆ txUserResetIn

|

Port |

Definition at line 222 of file Gtx7Core.vhd.

◆ txResetDoneOut

|

Port |

Definition at line 223 of file Gtx7Core.vhd.

◆ txDataIn

|

Port |

Definition at line 226 of file Gtx7Core.vhd.

◆ txCharIsKIn

|

Port |

Definition at line 227 of file Gtx7Core.vhd.

◆ txBufStatusOut

|

Port |

Definition at line 228 of file Gtx7Core.vhd.

◆ txPolarityIn

|

Port |

Definition at line 229 of file Gtx7Core.vhd.

◆ txPowerDown

|

Port |

Definition at line 231 of file Gtx7Core.vhd.

◆ rxPowerDown

|

Port |

Definition at line 232 of file Gtx7Core.vhd.

◆ loopbackIn

|

Port |

Definition at line 233 of file Gtx7Core.vhd.

◆ txPreCursor

|

Port |

Definition at line 234 of file Gtx7Core.vhd.

◆ txPostCursor

|

Port |

Definition at line 235 of file Gtx7Core.vhd.

◆ txDiffCtrl

|

Port |

Definition at line 236 of file Gtx7Core.vhd.

◆ drpClk

Definition at line 238 of file Gtx7Core.vhd.

◆ drpRdy

Definition at line 239 of file Gtx7Core.vhd.

◆ drpEn

Definition at line 240 of file Gtx7Core.vhd.

◆ drpWe

Definition at line 241 of file Gtx7Core.vhd.

◆ drpAddr

Definition at line 242 of file Gtx7Core.vhd.

◆ drpDi

Definition at line 243 of file Gtx7Core.vhd.

◆ drpDo

Definition at line 244 of file Gtx7Core.vhd.

◆ ieee

|

Library |

Definition at line 18 of file Gtx7Core.vhd.

◆ std_logic_1164

|

Package |

Definition at line 19 of file Gtx7Core.vhd.

◆ math_real

|

Package |

Definition at line 20 of file Gtx7Core.vhd.

◆ StdRtlPkg

|

Package |

Definition at line 22 of file Gtx7Core.vhd.

◆ UNISIM

|

Library |

Definition at line 24 of file Gtx7Core.vhd.

◆ VCOMPONENTS

|

Package |

Definition at line 25 of file Gtx7Core.vhd.

The documentation for this class was generated from the following file:

- xilinx/7Series/gtx7/rtl/Gtx7Core.vhd