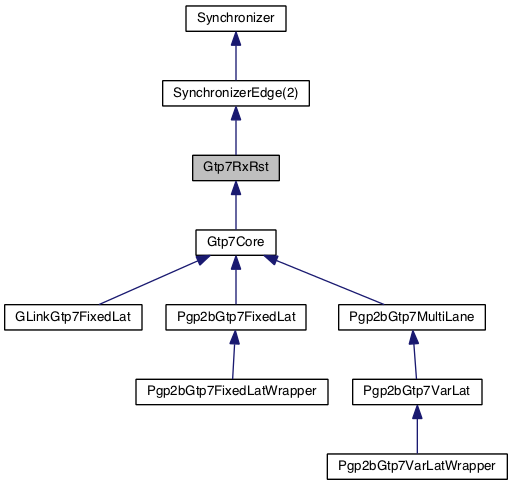

Inheritance diagram for Gtp7RxRst:

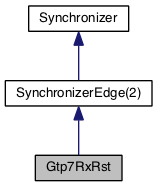

Inheritance diagram for Gtp7RxRst: Collaboration diagram for Gtp7RxRst:

Collaboration diagram for Gtp7RxRst:Entities | |

| RTL | architecture |

Libraries | |

| ieee | |

Use Clauses | |

| std_logic_1164 | |

| std_logic_arith | |

| std_logic_unsigned | |

Generics | |

| TPD_G | time := 1 ns |

| SIMULATION_G | boolean := false |

| STABLE_CLOCK_PERIOD | integer range 4 to 20 := 8 |

| RETRY_COUNTER_BITWIDTH | integer range 2 to 8 := 8 |

| TX_PLL0_USED | boolean := false |

| RX_PLL0_USED | boolean := false |

Ports | |

| STABLE_CLOCK | in std_logic |

| RXUSERCLK | in std_logic |

| SOFT_RESET | in std_logic |

| RXPMARESETDONE | in std_logic |

| RXOUTCLK | in std_logic |

| PLL0REFCLKLOST | in std_logic |

| PLL1REFCLKLOST | in std_logic |

| PLL0LOCK | in std_logic |

| PLL1LOCK | in std_logic |

| RXRESETDONE | in std_logic |

| MMCM_LOCK | in std_logic |

| RECCLK_STABLE | in std_logic |

| RECCLK_MONITOR_RESTART | in std_logic := ' 0 ' |

| DATA_VALID | in std_logic |

| TXUSERRDY | in std_logic |

| DONT_RESET_ON_DATA_ERROR | in std_logic := ' 0 ' |

| GTRXRESET | out std_logic := ' 0 ' |

| MMCM_RESET | out std_logic := ' 1 ' |

| PLL0_RESET | out std_logic := ' 0 ' |

| PLL1_RESET | out std_logic := ' 0 ' |

| RX_FSM_RESET_DONE | out std_logic |

| RXUSERRDY | out std_logic := ' 0 ' |

| RUN_PHALIGNMENT | out std_logic |

| PHALIGNMENT_DONE | in std_logic |

| RESET_PHALIGNMENT | out std_logic := ' 0 ' |

| RXDFEAGCHOLD | out std_logic := ' 0 ' |

| RXDFELFHOLD | out std_logic := ' 0 ' |

| RXLPMLFHOLD | out std_logic := ' 0 ' |

| RXLPMHFHOLD | out std_logic := ' 0 ' |

| RETRY_COUNTER | out std_logic_vector ( RETRY_COUNTER_BITWIDTH - 1 downto 0 ) := ( others = > ' 0 ' ) |

Detailed Description

- See also

- entity

Definition at line 77 of file Gtp7RxRst.vhd.

Member Data Documentation

◆ TPD_G

|

Generic |

Definition at line 79 of file Gtp7RxRst.vhd.

◆ SIMULATION_G

|

Generic |

Definition at line 80 of file Gtp7RxRst.vhd.

◆ STABLE_CLOCK_PERIOD

|

Generic |

Definition at line 81 of file Gtp7RxRst.vhd.

◆ RETRY_COUNTER_BITWIDTH

|

Generic |

Definition at line 82 of file Gtp7RxRst.vhd.

◆ TX_PLL0_USED

|

Generic |

Definition at line 83 of file Gtp7RxRst.vhd.

◆ RX_PLL0_USED

|

Generic |

Definition at line 85 of file Gtp7RxRst.vhd.

◆ STABLE_CLOCK

|

Port |

Definition at line 86 of file Gtp7RxRst.vhd.

◆ RXUSERCLK

|

Port |

Definition at line 88 of file Gtp7RxRst.vhd.

◆ SOFT_RESET

|

Port |

Definition at line 89 of file Gtp7RxRst.vhd.

◆ RXPMARESETDONE

|

Port |

Definition at line 90 of file Gtp7RxRst.vhd.

◆ RXOUTCLK

|

Port |

Definition at line 91 of file Gtp7RxRst.vhd.

◆ PLL0REFCLKLOST

|

Port |

Definition at line 92 of file Gtp7RxRst.vhd.

◆ PLL1REFCLKLOST

|

Port |

Definition at line 93 of file Gtp7RxRst.vhd.

◆ PLL0LOCK

|

Port |

Definition at line 94 of file Gtp7RxRst.vhd.

◆ PLL1LOCK

|

Port |

Definition at line 95 of file Gtp7RxRst.vhd.

◆ RXRESETDONE

|

Port |

Definition at line 96 of file Gtp7RxRst.vhd.

◆ MMCM_LOCK

|

Port |

Definition at line 97 of file Gtp7RxRst.vhd.

◆ RECCLK_STABLE

|

Port |

Definition at line 98 of file Gtp7RxRst.vhd.

◆ RECCLK_MONITOR_RESTART

|

Port |

Definition at line 99 of file Gtp7RxRst.vhd.

◆ DATA_VALID

|

Port |

Definition at line 100 of file Gtp7RxRst.vhd.

◆ TXUSERRDY

|

Port |

Definition at line 101 of file Gtp7RxRst.vhd.

◆ DONT_RESET_ON_DATA_ERROR

|

Port |

Definition at line 102 of file Gtp7RxRst.vhd.

◆ GTRXRESET

|

Port |

Definition at line 103 of file Gtp7RxRst.vhd.

◆ MMCM_RESET

|

Port |

Definition at line 104 of file Gtp7RxRst.vhd.

◆ PLL0_RESET

|

Port |

Definition at line 105 of file Gtp7RxRst.vhd.

◆ PLL1_RESET

|

Port |

Definition at line 106 of file Gtp7RxRst.vhd.

◆ RX_FSM_RESET_DONE

|

Port |

Definition at line 107 of file Gtp7RxRst.vhd.

◆ RXUSERRDY

|

Port |

Definition at line 108 of file Gtp7RxRst.vhd.

◆ RUN_PHALIGNMENT

|

Port |

Definition at line 109 of file Gtp7RxRst.vhd.

◆ PHALIGNMENT_DONE

|

Port |

Definition at line 110 of file Gtp7RxRst.vhd.

◆ RESET_PHALIGNMENT

|

Port |

Definition at line 111 of file Gtp7RxRst.vhd.

◆ RXDFEAGCHOLD

|

Port |

Definition at line 112 of file Gtp7RxRst.vhd.

◆ RXDFELFHOLD

|

Port |

Definition at line 113 of file Gtp7RxRst.vhd.

◆ RXLPMLFHOLD

|

Port |

Definition at line 114 of file Gtp7RxRst.vhd.

◆ RXLPMHFHOLD

|

Port |

Definition at line 115 of file Gtp7RxRst.vhd.

◆ RETRY_COUNTER

|

Port |

Definition at line 118 of file Gtp7RxRst.vhd.

◆ ieee

|

Library |

Definition at line 70 of file Gtp7RxRst.vhd.

◆ std_logic_1164

|

Package |

Definition at line 71 of file Gtp7RxRst.vhd.

◆ std_logic_arith

|

Package |

Definition at line 72 of file Gtp7RxRst.vhd.

◆ std_logic_unsigned

|

Package |

Definition at line 73 of file Gtp7RxRst.vhd.

The documentation for this class was generated from the following file:

- xilinx/7Series/gtp7/rtl/Gtp7RxRst.vhd