Inheritance diagram for AxiStreamFifoV2:

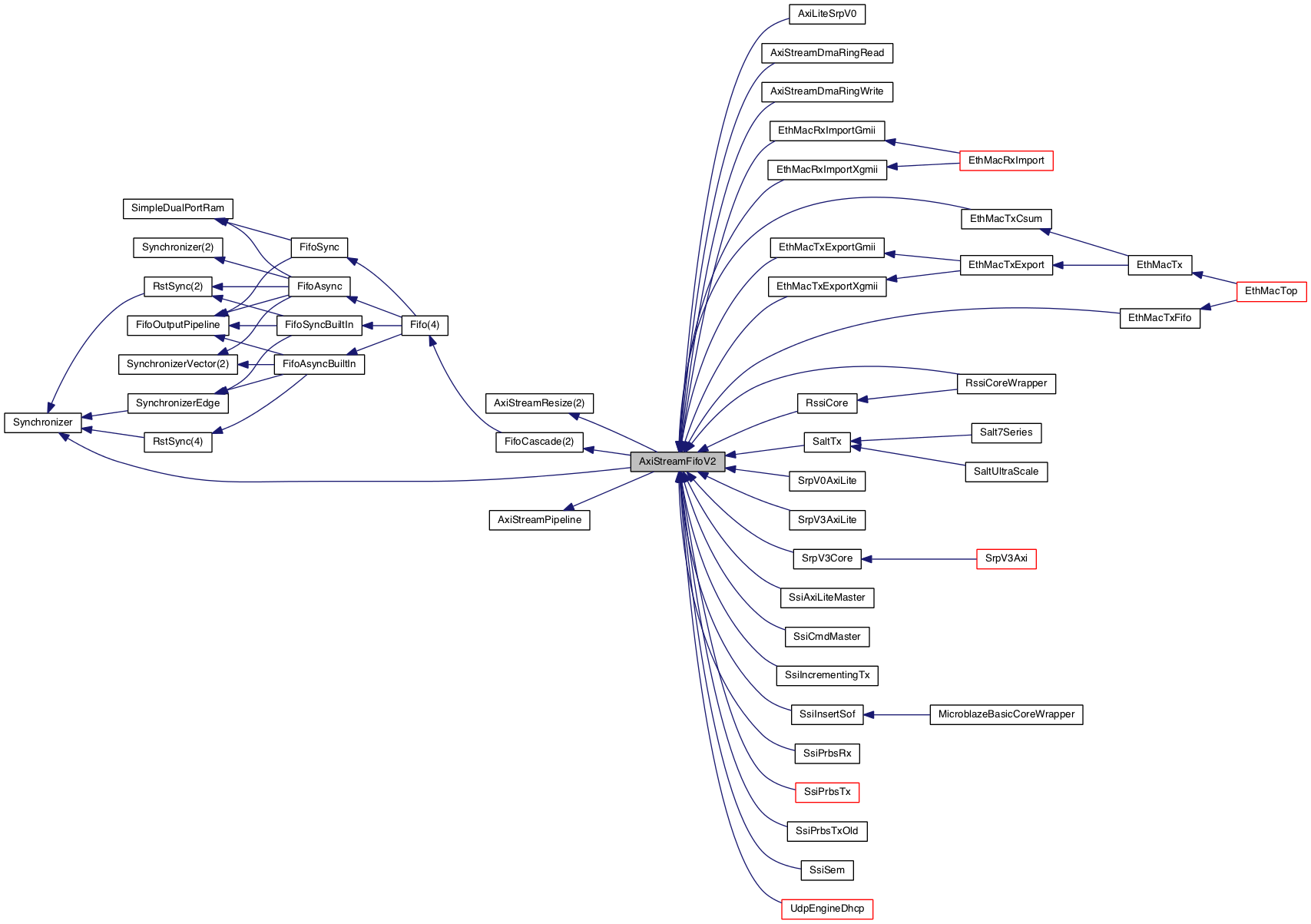

Inheritance diagram for AxiStreamFifoV2: Collaboration diagram for AxiStreamFifoV2:

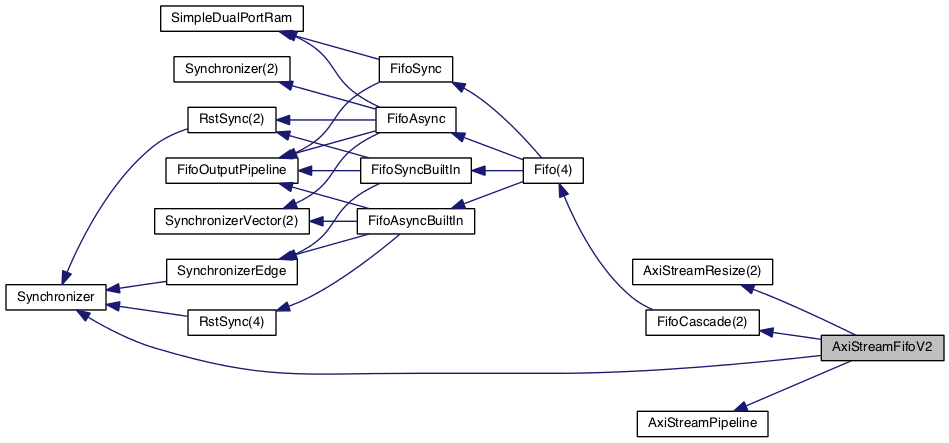

Collaboration diagram for AxiStreamFifoV2:Entities | |

| rtl | architecture |

Libraries | |

| ieee | |

Use Clauses | |

| std_logic_1164 | |

| std_logic_unsigned | |

| std_logic_arith | |

| StdRtlPkg | Package <StdRtlPkg> |

| AxiStreamPkg | Package <AxiStreamPkg> |

Generics | |

| TPD_G | time := 1 ns |

| INT_PIPE_STAGES_G | natural range 0 to 16 := 0 |

| PIPE_STAGES_G | natural range 0 to 16 := 1 |

| SLAVE_READY_EN_G | boolean := true |

| VALID_THOLD_G | integer range 0 to ( 2 ** 24 ) := 1 |

| VALID_BURST_MODE_G | boolean := false |

| BRAM_EN_G | boolean := true |

| XIL_DEVICE_G | string := " 7SERIES " |

| USE_BUILT_IN_G | boolean := false |

| GEN_SYNC_FIFO_G | boolean := false |

| ALTERA_SYN_G | boolean := false |

| ALTERA_RAM_G | string := " M9K " |

| CASCADE_SIZE_G | integer range 1 to ( 2 ** 24 ) := 1 |

| FIFO_ADDR_WIDTH_G | integer range 4 to 48 := 9 |

| FIFO_FIXED_THRESH_G | boolean := true |

| FIFO_PAUSE_THRESH_G | integer range 1 to ( 2 ** 24 ) := 1 |

| INT_WIDTH_SELECT_G | string := " WIDE " |

| INT_DATA_WIDTH_G | natural range 1 to 16 := 16 |

| LAST_FIFO_ADDR_WIDTH_G | integer range 0 to 48 := 0 |

| CASCADE_PAUSE_SEL_G | integer range 0 to ( 2 ** 24 ) := 0 |

| SLAVE_AXI_CONFIG_G | AxiStreamConfigType := AXI_STREAM_CONFIG_INIT_C |

| MASTER_AXI_CONFIG_G | AxiStreamConfigType := AXI_STREAM_CONFIG_INIT_C |

Ports | |

| sAxisClk | in sl |

| sAxisRst | in sl |

| sAxisMaster | in AxiStreamMasterType |

| sAxisSlave | out AxiStreamSlaveType |

| sAxisCtrl | out AxiStreamCtrlType |

| fifoPauseThresh | in slv ( FIFO_ADDR_WIDTH_G - 1 downto 0 ) := ( others = > ' 1 ' ) |

| mAxisClk | in sl |

| mAxisRst | in sl |

| mAxisMaster | out AxiStreamMasterType |

| mAxisSlave | in AxiStreamSlaveType |

| mTLastTUser | out slv ( 7 downto 0 ) |

Detailed Description

- See also

- entity

Definition at line 31 of file AxiStreamFifoV2.vhd.

Member Data Documentation

◆ TPD_G

|

Generic |

Definition at line 35 of file AxiStreamFifoV2.vhd.

◆ INT_PIPE_STAGES_G

|

Generic |

Definition at line 36 of file AxiStreamFifoV2.vhd.

◆ PIPE_STAGES_G

|

Generic |

Definition at line 37 of file AxiStreamFifoV2.vhd.

◆ SLAVE_READY_EN_G

|

Generic |

Definition at line 38 of file AxiStreamFifoV2.vhd.

◆ VALID_THOLD_G

|

Generic |

Definition at line 41 of file AxiStreamFifoV2.vhd.

◆ VALID_BURST_MODE_G

|

Generic |

Definition at line 44 of file AxiStreamFifoV2.vhd.

◆ BRAM_EN_G

|

Generic |

Definition at line 46 of file AxiStreamFifoV2.vhd.

◆ XIL_DEVICE_G

|

Generic |

Definition at line 47 of file AxiStreamFifoV2.vhd.

◆ USE_BUILT_IN_G

|

Generic |

Definition at line 48 of file AxiStreamFifoV2.vhd.

◆ GEN_SYNC_FIFO_G

|

Generic |

Definition at line 49 of file AxiStreamFifoV2.vhd.

◆ ALTERA_SYN_G

|

Generic |

Definition at line 50 of file AxiStreamFifoV2.vhd.

◆ ALTERA_RAM_G

|

Generic |

Definition at line 51 of file AxiStreamFifoV2.vhd.

◆ CASCADE_SIZE_G

|

Generic |

Definition at line 52 of file AxiStreamFifoV2.vhd.

◆ FIFO_ADDR_WIDTH_G

|

Generic |

Definition at line 53 of file AxiStreamFifoV2.vhd.

◆ FIFO_FIXED_THRESH_G

|

Generic |

Definition at line 54 of file AxiStreamFifoV2.vhd.

◆ FIFO_PAUSE_THRESH_G

|

Generic |

Definition at line 55 of file AxiStreamFifoV2.vhd.

◆ INT_WIDTH_SELECT_G

|

Generic |

Definition at line 60 of file AxiStreamFifoV2.vhd.

◆ INT_DATA_WIDTH_G

|

Generic |

Definition at line 61 of file AxiStreamFifoV2.vhd.

◆ LAST_FIFO_ADDR_WIDTH_G

|

Generic |

Definition at line 67 of file AxiStreamFifoV2.vhd.

◆ CASCADE_PAUSE_SEL_G

|

Generic |

Definition at line 70 of file AxiStreamFifoV2.vhd.

◆ SLAVE_AXI_CONFIG_G

Definition at line 73 of file AxiStreamFifoV2.vhd.

◆ MASTER_AXI_CONFIG_G

Definition at line 75 of file AxiStreamFifoV2.vhd.

◆ sAxisClk

Definition at line 79 of file AxiStreamFifoV2.vhd.

◆ sAxisRst

Definition at line 80 of file AxiStreamFifoV2.vhd.

◆ sAxisMaster

|

Port |

Definition at line 81 of file AxiStreamFifoV2.vhd.

◆ sAxisSlave

|

Port |

Definition at line 82 of file AxiStreamFifoV2.vhd.

◆ sAxisCtrl

|

Port |

Definition at line 83 of file AxiStreamFifoV2.vhd.

◆ fifoPauseThresh

|

Port |

Definition at line 87 of file AxiStreamFifoV2.vhd.

◆ mAxisClk

Definition at line 90 of file AxiStreamFifoV2.vhd.

◆ mAxisRst

Definition at line 91 of file AxiStreamFifoV2.vhd.

◆ mAxisMaster

|

Port |

Definition at line 92 of file AxiStreamFifoV2.vhd.

◆ mAxisSlave

|

Port |

Definition at line 93 of file AxiStreamFifoV2.vhd.

◆ mTLastTUser

|

Port |

Definition at line 94 of file AxiStreamFifoV2.vhd.

◆ ieee

|

Library |

Definition at line 21 of file AxiStreamFifoV2.vhd.

◆ std_logic_1164

|

Package |

Definition at line 22 of file AxiStreamFifoV2.vhd.

◆ std_logic_unsigned

|

Package |

Definition at line 23 of file AxiStreamFifoV2.vhd.

◆ std_logic_arith

|

Package |

Definition at line 24 of file AxiStreamFifoV2.vhd.

◆ StdRtlPkg

|

Package |

Definition at line 26 of file AxiStreamFifoV2.vhd.

◆ AxiStreamPkg

|

Package |

Definition at line 27 of file AxiStreamFifoV2.vhd.

The documentation for this class was generated from the following file:

- axi/rtl/AxiStreamFifoV2.vhd