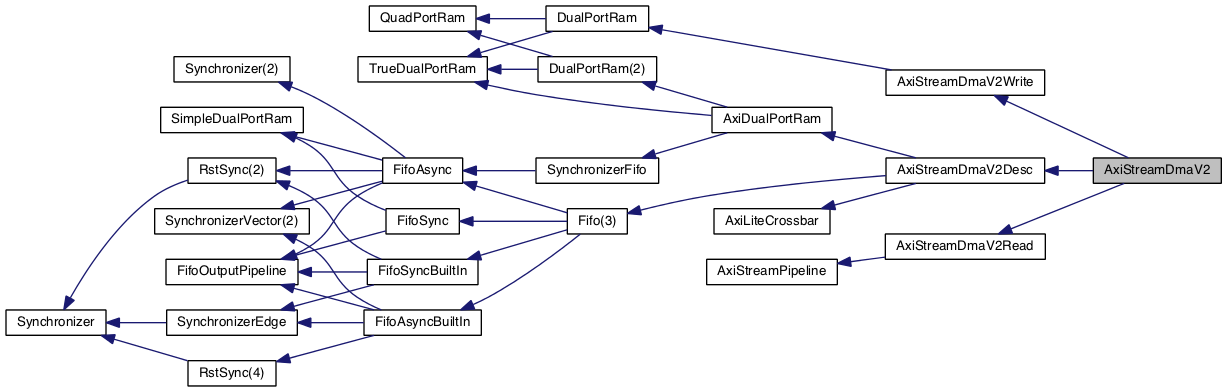

Inheritance diagram for AxiStreamDmaV2:

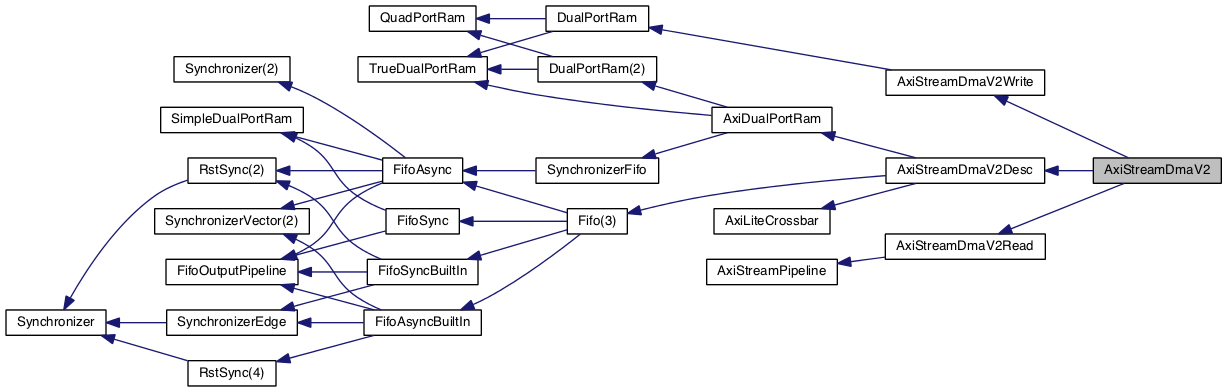

Inheritance diagram for AxiStreamDmaV2: Collaboration diagram for AxiStreamDmaV2:

Collaboration diagram for AxiStreamDmaV2:Entities | |

| structure | architecture |

Libraries | |

| ieee | |

Use Clauses | |

| std_logic_1164 | |

| std_logic_arith | |

| std_logic_unsigned | |

| StdRtlPkg | Package <StdRtlPkg> |

| AxiStreamPkg | Package <AxiStreamPkg> |

| AxiLitePkg | Package <AxiLitePkg> |

| AxiPkg | Package <AxiPkg> |

| AxiDmaPkg | Package <AxiDmaPkg> |

Generics | |

| TPD_G | time := 1 ns |

| DESC_AWIDTH_G | integer range 4 to 12 := 12 |

| AXIL_BASE_ADDR_G | slv ( 31 downto 0 ) := x " 00000000 " |

| AXI_ERROR_RESP_G | slv ( 1 downto 0 ) := AXI_RESP_OK_C |

| AXI_READY_EN_G | boolean := false |

| AXIS_READY_EN_G | boolean := false |

| AXIS_CONFIG_G | AxiStreamConfigType := AXI_STREAM_CONFIG_INIT_C |

| AXI_DESC_CONFIG_G | AxiConfigType := AXI_CONFIG_INIT_C |

| AXI_DMA_CONFIG_G | AxiConfigType := AXI_CONFIG_INIT_C |

| CHAN_COUNT_G | integer range 1 to 16 := 1 |

| BURST_BYTES_G | integer range 1 to 4096 := 4096 |

| RD_PIPE_STAGES_G | natural := 1 |

| RD_PEND_THRESH_G | natural := 0 |

Ports | |

| axiClk | in sl |

| axiRst | in sl |

| axilReadMaster | in AxiLiteReadMasterType |

| axilReadSlave | out AxiLiteReadSlaveType |

| axilWriteMaster | in AxiLiteWriteMasterType |

| axilWriteSlave | out AxiLiteWriteSlaveType |

| interrupt | out sl |

| online | out slv ( CHAN_COUNT_G - 1 downto 0 ) |

| acknowledge | out slv ( CHAN_COUNT_G - 1 downto 0 ) |

| sAxisMaster | in AxiStreamMasterArray ( CHAN_COUNT_G - 1 downto 0 ) |

| sAxisSlave | out AxiStreamSlaveArray ( CHAN_COUNT_G - 1 downto 0 ) |

| mAxisMaster | out AxiStreamMasterArray ( CHAN_COUNT_G - 1 downto 0 ) |

| mAxisSlave | in AxiStreamSlaveArray ( CHAN_COUNT_G - 1 downto 0 ) |

| mAxisCtrl | in AxiStreamCtrlArray ( CHAN_COUNT_G - 1 downto 0 ) |

| axiReadMaster | out AxiReadMasterArray ( CHAN_COUNT_G downto 0 ) |

| axiReadSlave | in AxiReadSlaveArray ( CHAN_COUNT_G downto 0 ) |

| axiWriteMaster | out AxiWriteMasterArray ( CHAN_COUNT_G downto 0 ) |

| axiWriteSlave | in AxiWriteSlaveArray ( CHAN_COUNT_G downto 0 ) |

| axiWriteCtrl | in AxiCtrlArray ( CHAN_COUNT_G downto 0 ) |

Detailed Description

- See also

- entity

Definition at line 32 of file AxiStreamDmaV2.vhd.

Member Data Documentation

◆ TPD_G

|

Generic |

Definition at line 34 of file AxiStreamDmaV2.vhd.

◆ DESC_AWIDTH_G

|

Generic |

Definition at line 35 of file AxiStreamDmaV2.vhd.

◆ AXIL_BASE_ADDR_G

|

Generic |

Definition at line 36 of file AxiStreamDmaV2.vhd.

◆ AXI_ERROR_RESP_G

|

Generic |

Definition at line 37 of file AxiStreamDmaV2.vhd.

◆ AXI_READY_EN_G

|

Generic |

Definition at line 38 of file AxiStreamDmaV2.vhd.

◆ AXIS_READY_EN_G

|

Generic |

Definition at line 39 of file AxiStreamDmaV2.vhd.

◆ AXIS_CONFIG_G

Definition at line 40 of file AxiStreamDmaV2.vhd.

◆ AXI_DESC_CONFIG_G

|

Generic |

Definition at line 41 of file AxiStreamDmaV2.vhd.

◆ AXI_DMA_CONFIG_G

|

Generic |

Definition at line 42 of file AxiStreamDmaV2.vhd.

◆ CHAN_COUNT_G

|

Generic |

Definition at line 43 of file AxiStreamDmaV2.vhd.

◆ BURST_BYTES_G

|

Generic |

Definition at line 44 of file AxiStreamDmaV2.vhd.

◆ RD_PIPE_STAGES_G

|

Generic |

Definition at line 45 of file AxiStreamDmaV2.vhd.

◆ RD_PEND_THRESH_G

|

Generic |

Definition at line 46 of file AxiStreamDmaV2.vhd.

◆ axiClk

Definition at line 49 of file AxiStreamDmaV2.vhd.

◆ axiRst

Definition at line 50 of file AxiStreamDmaV2.vhd.

◆ axilReadMaster

|

Port |

Definition at line 52 of file AxiStreamDmaV2.vhd.

◆ axilReadSlave

|

Port |

Definition at line 53 of file AxiStreamDmaV2.vhd.

◆ axilWriteMaster

Definition at line 54 of file AxiStreamDmaV2.vhd.

◆ axilWriteSlave

|

Port |

Definition at line 55 of file AxiStreamDmaV2.vhd.

◆ interrupt

Definition at line 56 of file AxiStreamDmaV2.vhd.

◆ online

|

Port |

Definition at line 57 of file AxiStreamDmaV2.vhd.

◆ acknowledge

|

Port |

Definition at line 58 of file AxiStreamDmaV2.vhd.

◆ sAxisMaster

|

Port |

Definition at line 60 of file AxiStreamDmaV2.vhd.

◆ sAxisSlave

|

Port |

Definition at line 61 of file AxiStreamDmaV2.vhd.

◆ mAxisMaster

|

Port |

Definition at line 62 of file AxiStreamDmaV2.vhd.

◆ mAxisSlave

|

Port |

Definition at line 63 of file AxiStreamDmaV2.vhd.

◆ mAxisCtrl

|

Port |

Definition at line 64 of file AxiStreamDmaV2.vhd.

◆ axiReadMaster

|

Port |

Definition at line 66 of file AxiStreamDmaV2.vhd.

◆ axiReadSlave

|

Port |

Definition at line 67 of file AxiStreamDmaV2.vhd.

◆ axiWriteMaster

|

Port |

Definition at line 68 of file AxiStreamDmaV2.vhd.

◆ axiWriteSlave

|

Port |

Definition at line 69 of file AxiStreamDmaV2.vhd.

◆ axiWriteCtrl

|

Port |

Definition at line 70 of file AxiStreamDmaV2.vhd.

◆ ieee

|

Library |

Definition at line 19 of file AxiStreamDmaV2.vhd.

◆ std_logic_1164

|

Package |

Definition at line 20 of file AxiStreamDmaV2.vhd.

◆ std_logic_arith

|

Package |

Definition at line 21 of file AxiStreamDmaV2.vhd.

◆ std_logic_unsigned

|

Package |

Definition at line 22 of file AxiStreamDmaV2.vhd.

◆ StdRtlPkg

|

Package |

Definition at line 24 of file AxiStreamDmaV2.vhd.

◆ AxiStreamPkg

|

Package |

Definition at line 25 of file AxiStreamDmaV2.vhd.

◆ AxiLitePkg

|

Package |

Definition at line 26 of file AxiStreamDmaV2.vhd.

◆ AxiPkg

|

Package |

Definition at line 27 of file AxiStreamDmaV2.vhd.

◆ AxiDmaPkg

|

Package |

Definition at line 28 of file AxiStreamDmaV2.vhd.

The documentation for this class was generated from the following file:

- axi/rtl/AxiStreamDmaV2.vhd