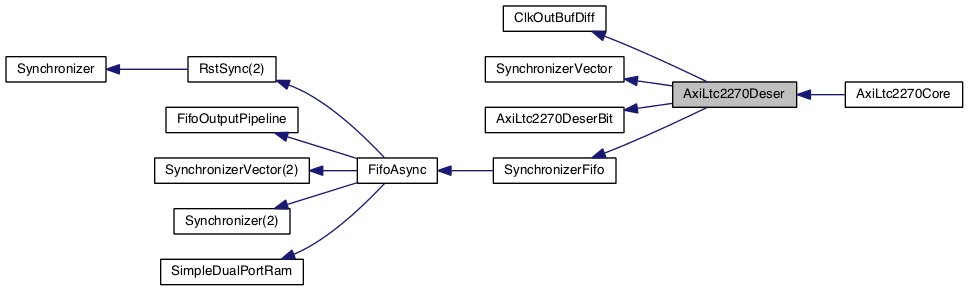

Inheritance diagram for AxiLtc2270Deser:

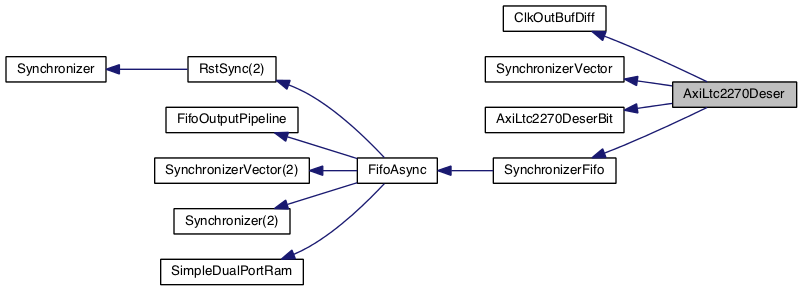

Inheritance diagram for AxiLtc2270Deser: Collaboration diagram for AxiLtc2270Deser:

Collaboration diagram for AxiLtc2270Deser:Entities | |

| rtl | architecture |

Libraries | |

| ieee | |

| unisim | |

Use Clauses | |

| std_logic_1164 | |

| std_logic_unsigned | |

| std_logic_arith | |

| StdRtlPkg | Package <StdRtlPkg> |

| AxiLtc2270Pkg | Package <AxiLtc2270Pkg> |

| vcomponents | |

Generics | |

| TPD_G | time := 1 ns |

| DELAY_INIT_G | Slv5VectorArray ( 0 to 1 , 0 to 7 ) := ( others = > ( others = > ( others = > ' 0 ' ) ) ) |

| IODELAY_GROUP_G | string := " AXI_LTC2270_IODELAY_GRP " |

Ports | |

| clkInP | in sl |

| clkInN | in sl |

| clkOutP | out sl |

| clkOutN | out sl |

| dataP | in Slv8Array ( 0 to 1 ) |

| dataN | in Slv8Array ( 0 to 1 ) |

| orP | in sl |

| orN | in sl |

| adcValid | out slv ( 0 to 1 ) |

| adcData | out Slv16Array ( 0 to 1 ) |

| dmode | in slv ( 1 downto 0 ) |

| delayin | in AxiLtc2270DelayInType |

| delayOut | out AxiLtc2270DelayOutType |

| axiClk | in sl |

| axiRst | in sl |

| adcClk | in sl |

| refclk200MHz | in sl |

Detailed Description

- See also

- entity

Definition at line 31 of file AxiLtc2270Deser.vhd.

Member Data Documentation

◆ TPD_G

|

Generic |

Definition at line 33 of file AxiLtc2270Deser.vhd.

◆ DELAY_INIT_G

|

Generic |

Definition at line 34 of file AxiLtc2270Deser.vhd.

◆ IODELAY_GROUP_G

|

Generic |

Definition at line 35 of file AxiLtc2270Deser.vhd.

◆ clkInP

Definition at line 38 of file AxiLtc2270Deser.vhd.

◆ clkInN

Definition at line 39 of file AxiLtc2270Deser.vhd.

◆ clkOutP

Definition at line 40 of file AxiLtc2270Deser.vhd.

◆ clkOutN

Definition at line 41 of file AxiLtc2270Deser.vhd.

◆ dataP

Definition at line 42 of file AxiLtc2270Deser.vhd.

◆ dataN

Definition at line 43 of file AxiLtc2270Deser.vhd.

◆ orP

Definition at line 44 of file AxiLtc2270Deser.vhd.

◆ orN

Definition at line 45 of file AxiLtc2270Deser.vhd.

◆ adcValid

Definition at line 47 of file AxiLtc2270Deser.vhd.

◆ adcData

|

Port |

Definition at line 48 of file AxiLtc2270Deser.vhd.

◆ dmode

Definition at line 50 of file AxiLtc2270Deser.vhd.

◆ delayin

|

Port |

Definition at line 52 of file AxiLtc2270Deser.vhd.

◆ delayOut

|

Port |

Definition at line 53 of file AxiLtc2270Deser.vhd.

◆ axiClk

Definition at line 55 of file AxiLtc2270Deser.vhd.

◆ axiRst

Definition at line 56 of file AxiLtc2270Deser.vhd.

◆ adcClk

Definition at line 57 of file AxiLtc2270Deser.vhd.

◆ refclk200MHz

|

Port |

Definition at line 58 of file AxiLtc2270Deser.vhd.

◆ ieee

|

Library |

Definition at line 18 of file AxiLtc2270Deser.vhd.

◆ std_logic_1164

|

Package |

Definition at line 19 of file AxiLtc2270Deser.vhd.

◆ std_logic_unsigned

|

Package |

Definition at line 20 of file AxiLtc2270Deser.vhd.

◆ std_logic_arith

|

Package |

Definition at line 21 of file AxiLtc2270Deser.vhd.

◆ StdRtlPkg

|

Package |

Definition at line 23 of file AxiLtc2270Deser.vhd.

◆ AxiLtc2270Pkg

|

Package |

Definition at line 24 of file AxiLtc2270Deser.vhd.

◆ unisim

|

Library |

Definition at line 26 of file AxiLtc2270Deser.vhd.

◆ vcomponents

|

Package |

Definition at line 27 of file AxiLtc2270Deser.vhd.

The documentation for this class was generated from the following file:

- devices/Linear/lct2270/rtl/AxiLtc2270Deser.vhd