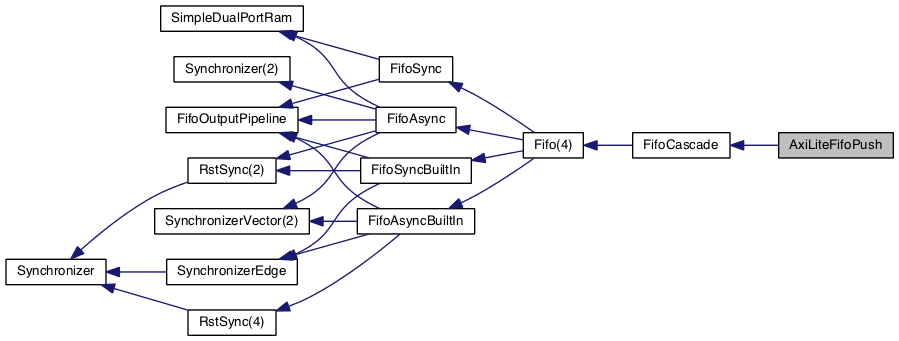

Inheritance diagram for AxiLiteFifoPush:

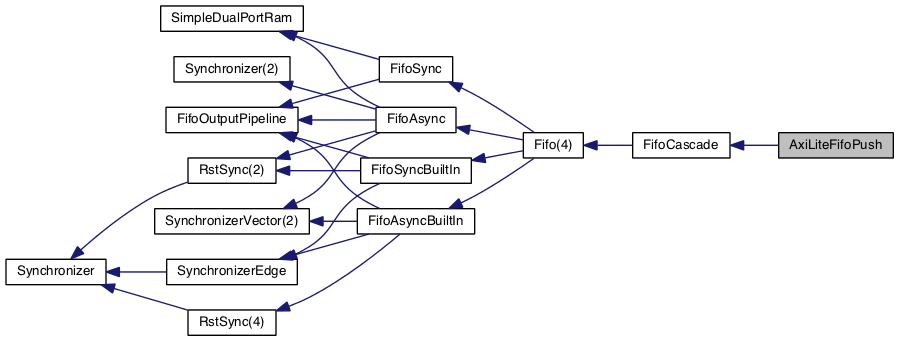

Inheritance diagram for AxiLiteFifoPush: Collaboration diagram for AxiLiteFifoPush:

Collaboration diagram for AxiLiteFifoPush:Entities | |

| structure | architecture |

Libraries | |

| ieee | |

Use Clauses | |

| std_logic_1164 | |

| STD_LOGIC_ARITH | |

| STD_LOGIC_UNSIGNED | |

| StdRtlPkg | Package <StdRtlPkg> |

| AxiLitePkg | Package <AxiLitePkg> |

Generics | |

| TPD_G | time := 1 ns |

| PUSH_FIFO_COUNT_G | positive := 1 |

| PUSH_SYNC_FIFO_G | boolean := false |

| PUSH_BRAM_EN_G | boolean := false |

| PUSH_ADDR_WIDTH_G | integer range 4 to 48 := 4 |

| ALTERA_SYN_G | boolean := false |

| ALTERA_RAM_G | string := " M9K " |

| USE_BUILT_IN_G | boolean := false |

| XIL_DEVICE_G | string := " 7SERIES " |

Ports | |

| axiClk | in sl |

| axiClkRst | in sl |

| axiReadMaster | in AxiLiteReadMasterType := AXI_LITE_READ_MASTER_INIT_C |

| axiReadSlave | out AxiLiteReadSlaveType |

| axiWriteMaster | in AxiLiteWriteMasterType |

| axiWriteSlave | out AxiLiteWriteSlaveType |

| pushFifoAFull | out slv ( PUSH_FIFO_COUNT_G - 1 downto 0 ) |

| pushFifoClk | in slv ( PUSH_FIFO_COUNT_G - 1 downto 0 ) |

| pushFifoRst | in slv ( PUSH_FIFO_COUNT_G - 1 downto 0 ) |

| pushFifoValid | out slv ( PUSH_FIFO_COUNT_G - 1 downto 0 ) |

| pushFifoDout | out Slv36Array ( PUSH_FIFO_COUNT_G - 1 downto 0 ) |

| pushFifoRead | in slv ( PUSH_FIFO_COUNT_G - 1 downto 0 ) |

Detailed Description

- See also

- entity

Definition at line 30 of file AxiLiteFifoPush.vhd.

Member Data Documentation

◆ TPD_G

|

Generic |

Definition at line 32 of file AxiLiteFifoPush.vhd.

◆ PUSH_FIFO_COUNT_G

|

Generic |

Definition at line 33 of file AxiLiteFifoPush.vhd.

◆ PUSH_SYNC_FIFO_G

|

Generic |

Definition at line 34 of file AxiLiteFifoPush.vhd.

◆ PUSH_BRAM_EN_G

|

Generic |

Definition at line 35 of file AxiLiteFifoPush.vhd.

◆ PUSH_ADDR_WIDTH_G

|

Generic |

Definition at line 36 of file AxiLiteFifoPush.vhd.

◆ ALTERA_SYN_G

|

Generic |

Definition at line 37 of file AxiLiteFifoPush.vhd.

◆ ALTERA_RAM_G

|

Generic |

Definition at line 38 of file AxiLiteFifoPush.vhd.

◆ USE_BUILT_IN_G

|

Generic |

Definition at line 39 of file AxiLiteFifoPush.vhd.

◆ XIL_DEVICE_G

|

Generic |

Definition at line 41 of file AxiLiteFifoPush.vhd.

◆ axiClk

Definition at line 45 of file AxiLiteFifoPush.vhd.

◆ axiClkRst

Definition at line 46 of file AxiLiteFifoPush.vhd.

◆ axiReadMaster

Definition at line 47 of file AxiLiteFifoPush.vhd.

◆ axiReadSlave

|

Port |

Definition at line 48 of file AxiLiteFifoPush.vhd.

◆ axiWriteMaster

|

Port |

Definition at line 49 of file AxiLiteFifoPush.vhd.

◆ axiWriteSlave

|

Port |

Definition at line 50 of file AxiLiteFifoPush.vhd.

◆ pushFifoAFull

|

Port |

Definition at line 51 of file AxiLiteFifoPush.vhd.

◆ pushFifoClk

|

Port |

Definition at line 54 of file AxiLiteFifoPush.vhd.

◆ pushFifoRst

|

Port |

Definition at line 55 of file AxiLiteFifoPush.vhd.

◆ pushFifoValid

|

Port |

Definition at line 56 of file AxiLiteFifoPush.vhd.

◆ pushFifoDout

|

Port |

Definition at line 57 of file AxiLiteFifoPush.vhd.

◆ pushFifoRead

|

Port |

Definition at line 59 of file AxiLiteFifoPush.vhd.

◆ ieee

|

Library |

Definition at line 20 of file AxiLiteFifoPush.vhd.

◆ std_logic_1164

|

Package |

Definition at line 21 of file AxiLiteFifoPush.vhd.

◆ STD_LOGIC_ARITH

|

Package |

Definition at line 22 of file AxiLiteFifoPush.vhd.

◆ STD_LOGIC_UNSIGNED

|

Package |

Definition at line 23 of file AxiLiteFifoPush.vhd.

◆ StdRtlPkg

|

Package |

Definition at line 25 of file AxiLiteFifoPush.vhd.

◆ AxiLitePkg

|

Package |

Definition at line 26 of file AxiLiteFifoPush.vhd.

The documentation for this class was generated from the following file:

- axi/rtl/AxiLiteFifoPush.vhd