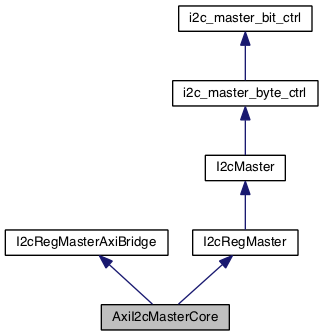

Inheritance diagram for AxiI2cMasterCore:

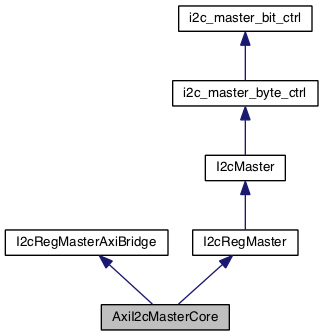

Inheritance diagram for AxiI2cMasterCore: Collaboration diagram for AxiI2cMasterCore:

Collaboration diagram for AxiI2cMasterCore:Entities | |

| mapping | architecture |

Libraries | |

| ieee | |

| unisim | |

Use Clauses | |

| std_logic_1164 | |

| StdRtlPkg | Package <StdRtlPkg> |

| AxiLitePkg | Package <AxiLitePkg> |

| I2cPkg | Package <I2cPkg> |

| AxiI2cMasterPkg | Package <AxiI2cMasterPkg> |

| vcomponents | |

Generics | |

| TPD_G | time := 1 ns |

| DEVICE_MAP_G | I2cAxiLiteDevArray := I2C_AXIL_DEV_ARRAY_DEFAULT_C |

| AXI_CLK_FREQ_G | real := 200 . 0E + 6 |

| I2C_SCL_FREQ_G | real := 100 . 0E + 3 |

| I2C_MIN_PULSE_G | real := 100 . 0E - 9 |

| AXI_ERROR_RESP_G | slv ( 1 downto 0 ) := AXI_RESP_SLVERR_C |

Detailed Description

- See also

- entity

Definition at line 31 of file AxiI2cMasterCore.vhd.

Member Data Documentation

◆ TPD_G

|

Generic |

Definition at line 33 of file AxiI2cMasterCore.vhd.

◆ DEVICE_MAP_G

Definition at line 34 of file AxiI2cMasterCore.vhd.

◆ AXI_CLK_FREQ_G

|

Generic |

Definition at line 35 of file AxiI2cMasterCore.vhd.

◆ I2C_SCL_FREQ_G

|

Generic |

Definition at line 36 of file AxiI2cMasterCore.vhd.

◆ I2C_MIN_PULSE_G

|

Generic |

Definition at line 37 of file AxiI2cMasterCore.vhd.

◆ AXI_ERROR_RESP_G

|

Generic |

Definition at line 38 of file AxiI2cMasterCore.vhd.

◆ i2cInOut

|

Port |

Definition at line 41 of file AxiI2cMasterCore.vhd.

◆ axiReadMaster

|

Port |

Definition at line 43 of file AxiI2cMasterCore.vhd.

◆ axiReadSlave

|

Port |

Definition at line 44 of file AxiI2cMasterCore.vhd.

◆ axiWriteMaster

|

Port |

Definition at line 45 of file AxiI2cMasterCore.vhd.

◆ axiWriteSlave

|

Port |

Definition at line 46 of file AxiI2cMasterCore.vhd.

◆ axiClk

Definition at line 48 of file AxiI2cMasterCore.vhd.

◆ axiRst

Definition at line 49 of file AxiI2cMasterCore.vhd.

◆ ieee

|

Library |

Definition at line 18 of file AxiI2cMasterCore.vhd.

◆ std_logic_1164

|

Package |

Definition at line 19 of file AxiI2cMasterCore.vhd.

◆ StdRtlPkg

|

Package |

Definition at line 21 of file AxiI2cMasterCore.vhd.

◆ AxiLitePkg

|

Package |

Definition at line 22 of file AxiI2cMasterCore.vhd.

◆ I2cPkg

|

Package |

Definition at line 23 of file AxiI2cMasterCore.vhd.

◆ AxiI2cMasterPkg

|

Package |

Definition at line 24 of file AxiI2cMasterCore.vhd.

◆ unisim

|

Library |

Definition at line 26 of file AxiI2cMasterCore.vhd.

◆ vcomponents

|

Package |

Definition at line 27 of file AxiI2cMasterCore.vhd.

The documentation for this class was generated from the following file:

- protocols/i2c/rtl/AxiI2cMasterCore.vhd